# **Purdue University** Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

8-2-2013

# Interface studies of N-2 plasma-treated ZnSnO nanowire transistors using low-frequency noise measurements

Seongmin Kim Birck Nanotechnology Center, Purdue University, kim482@purdue.edu

Hwansoo Kim Kyonggi University

David B. Janes Birck Nanotechnology Center, Purdue University, janes@purdue.edu

Sanghyun Ju Kyonggi University

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub

Part of the <u>Nanoscience and Nanotechnology Commons</u>

Kim, Seongmin; Kim, Hwansoo; Janes, David B.; and Ju, Sanghyun, "Interface studies of N-2 plasma-treated ZnSnO nanowire transistors using low-frequency noise measurements" (2013). Birck and NCN Publications. Paper 1446. http://dx.doi.org/10.1088/0957-4484/24/30/305201

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

Home Search Collections Journals About Contact us My IOPscience

Interface studies of N<sub>2</sub> plasma-treated ZnSnO nanowire transistors using low-frequency noise measurements

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2013 Nanotechnology 24 305201

(http://iopscience.iop.org/0957-4484/24/30/305201)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 128.46.221.64

This content was downloaded on 29/10/2013 at 19:02

Please note that terms and conditions apply.

IOP PUBLISHING NANOTECHNOLOGY

Nanotechnology 24 (2013) 305201 (7pp)

doi:10.1088/0957-4484/24/30/305201

# Interface studies of $N_2$ plasma-treated ZnSnO nanowire transistors using low-frequency noise measurements

# Seongmin Kim<sup>1</sup>, Hwansoo Kim<sup>2</sup>, David B Janes<sup>1</sup> and Sanghyun Ju<sup>2</sup>

- <sup>1</sup> School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907, USA

- <sup>2</sup> Department of Physics, Kyonggi University, Suwon, Gyeonggi-Do, 443-760, Republic of Korea

E-mail: shju@kgu.ac.kr

Received 8 January 2013, in final form 9 May 2013 Published 27 June 2013 Online at stacks.iop.org/Nano/24/305201

# Abstract

Due to the large surface-to-volume ratio of nanowires, the quality of nanowire-insulator interfaces as well as the nanowire surface characteristics significantly influence the electrical characteristics of nanowire transistors (NWTs). To improve the electrical characteristics by doping or post-processing, it is important to evaluate the interface characteristics and stability of NWTs. In this study, we have synthesized ZnSnO (ZTO) nanowires using the chemical vapor deposition method, characterized the composition of ZTO nanowires using x-ray photoelectron spectroscopy, and fabricated ZTO NWTs. We have characterized the current-voltage characteristics and low-frequency noise of ZTO NWTs in order to investigate the effects of interface states on subthreshold slope (SS) and the noise before and after N<sub>2</sub> plasma treatments. The as-fabricated device exhibited a SS of 0.29 V/dec and Hooge parameter of  $\sim 1.20 \times 10^{-2}$ . Upon N<sub>2</sub> plasma treatment with N<sub>2</sub> gas flow rate of 40 sccm (20 sccm), the SS improved to 0.12 V/dec (0.21 V/dec) and the Hooge parameter decreased to  $\sim 4.99 \times 10^{-3}$  (8.14  $\times$  10<sup>-3</sup>). The interface trap densities inferred from both SS and low-frequency noise decrease upon plasma treatment, with the highest flow rate yielding the smallest trap density. These results demonstrate that the N<sub>2</sub> plasma treatment decreases the interface trap states and defects on ZTO nanowires, thereby enabling the fabrication of high-quality nanowire interfaces.

(Some figures may appear in colour only in the online journal)

## 1. Introduction

Due to several advantages of nanowires such as transparency, flexibility, low operating voltages, and low fabrication temperatures, various studies have considered their applications to the development of various electronic, display, thermoelectric, environmental, and sensor devices [1–4]. The scope of nanowire transistor (NWT) integration in semiconductor complementary metal—oxide—semiconductor (CMOS) circuits is also increasing along with the high demand for device downscaling. In particular, many studies have been conducted on the development of NWTs and circuits using wide band-gap semiconducting oxides such as

ZnO, SnO<sub>2</sub>, In<sub>2</sub>O<sub>3</sub>, and Zn<sub>2</sub>SnO<sub>4</sub> for applications including memory and displays [5–9]. However, in order to apply nanowires to practical and commercial devices, it is important to prioritize the optimization of the different characteristics required for various applications. For applications that require high performance, high current along with large mobility is essential. For low-power applications, low static power consumption at zero bias by achieving low off-current and steep subthreshold slope (SS) accompanied by threshold voltage ( $V_{\rm th}$ ) engineering is of great interest. For low-noise applications such as analog/mixed-signal circuits, low signal-to-noise ratio is essential for reliable device operation. Due to the large surface-to-volume ratio of the nanowires, nanowire

surface characteristics and nanowire-insulator interfaces are known to significantly influence the electrical characteristics of NWTs, which could potentially result in fluctuation of the device performance metrics such as SS,  $V_{th}$ , on/off current ratio  $(I_{\rm on}/I_{\rm off})$ , field effect mobility  $(\mu_{\rm eff})$ , and noise [10-13]. Hence, in order to achieve robust and stable device operation and improve the electrical characteristics of nanowires, it is important to evaluate and optimize the nanowire surface characteristics. Numerous studies have been performed to optimize the optical, chemical, and electrical characteristics of nanowires. Some studies have been conducted on controlling the characteristics by changing the nanowire growth temperatures and controlling the characteristics of grown nanowires through gas treatments, thermal annealing, or plasma treatments [14-17]. Other studies have focused on controlling the characteristics by changing the nanowire material through the doping of metals or rare-earth materials [18-20]. For instance, the electrical characteristics of ZnO nanowires—a representative oxide semiconductor—have been improved by Ni, Ga, and Sn doping [21-23]. Doping material or gas/plasma treatments influence the defects, such as oxygen vacancies, along with fixed charges and interface trap densities on the oxide nanowire surfaces. However, such nanowire transistors after optimization still exhibit large SS and low  $\mu_{eff}$  showing that there is much room for improvement.

Low-frequency (1/f, flicker) noise has traditionally been utilized as a qualitative and a semi-quantitative measure of the origin of the noise, and a reliability indicator for semiconductor devices. The use of 1/f noise as a defect characterization method has become more popular in recent years, since 1/f noise is more sensitive to traps and defects in highly scaled devices such as nanotube- or nanowire-based field effect transistors (FETs) where scattering from surface states is enhanced [24]. The 1/f noise that originates from the trapping and detrapping of carriers at the channel, oxide, and their interface, provides significant information regarding the densities of the interface (surface) states in nanoscale devices [25–28]. The reported Hooge parameters ( $\alpha_{\rm H}$ ) for non-Si nanowire transistors to date, however, are far higher than the ITRS 45 nm technology node requirement ( $\alpha_{\rm H} \sim$  $2.0 \times 10^{-4}$ ) indicating that further improvement in the interface quality is essential in order to achieve nanowire transistors that can be applied to commercial digital and analog circuits [11, 12, 40]. In this research, we synthesized ZnSnO (ZTO) nanowires using chemical vapor deposition (CVD), and then characterized the composition of ZTO nanowires using x-ray photoelectron spectroscopy (XPS). We then fabricated ZTO NWTs and investigated the changes in their characteristics during the N2 plasma treatment. We have examined the quality of the device interfaces in ZTO NWTs before and after the N<sub>2</sub> plasma treatment using the SS characteristics and 1/f noise measurements. This reveals that the N<sub>2</sub> plasma-treated ZTO NWTs show excellent device performance suitable for high-performance (high  $\mu_{eff}$ ), low-power (low SS,  $V_{\text{th}}$  near zero), and low-noise (low  $\alpha_{\text{H}}$ ) applications.

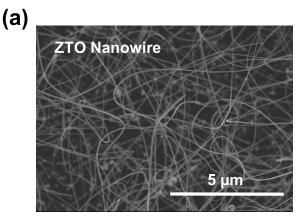

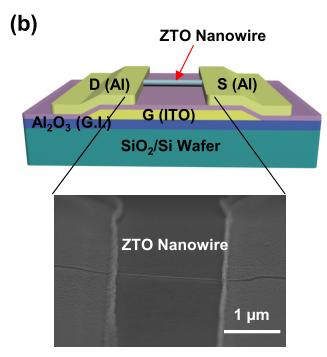

**Figure 1.** (a) FE-SEM image of as-grown ZTO nanowires. (b) Cross-sectional view of ZTO NWT with bottom gate structure. The inset shows the representative FE-SEM image of the nanowire channel region for a NWT with a single nanowire.

## 2. Experimental section

# 2.1. Synthesis of ZTO nanowires

The ZTO nanowires used in the fabrication process were grown by CVD method in a two-temperature-zone furnace that enabled us to adjust the source and substrate temperatures separately. We placed the combination of ZnO (99.999%, 0.6 g) and SnO (99.99%, 0.0149 g) in the source zone and located the SiO<sub>2</sub>/Si wafer uniformly coated with catalyst particles (gold nanoparticles, diameter: 20 nm) in the substrate zone. We then increased the temperature to 1090 °C in the source zone and to 720 °C in the substrate zone to facilitate the nanowire growth. Figure 1(a) shows the field emission scanning electron microscope (FE-SEM) image of the grown ZTO nanowires. The ZTO nanowires exhibited

uniform growth throughout the substrate and their average diameter and length were  $\sim$ 60 nm and  $\sim$ 5  $\mu$ m, respectively.

#### 2.2. Fabrication of ZTO NWTs

For the fabrication of the ZTO NWTs, we employed a separate SiO<sub>2</sub>/Si substrate and performed the following processes: bottom gate electrode formation, gate-dielectric layer formation, gate contact hole etching, nanowire dispersion, and source/drain electrode formation. First, the bottom gate electrode was formed by indium tin oxide (ITO, 100 nm) sputtering, and photolithographic patterning. Subsequently, a 30-nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric film was deposited by atomic layer deposition (ALD). The Al<sub>2</sub>O<sub>3</sub> layer was removed selectively at the gate electrode pad area in order to apply voltages to the gate electrode. After separating the ZTO nanowires from the growth substrate in isopropyl alcohol solution by ultrasonication, the nanowires were dispersed on the device substrate. As the last step, source-drain electrodes were formed by sputtering Al (thickness of 100 nm) and subsequent photolithographic patterning. Figure 1(b) shows the schematic diagram of the ZTO NWT and a representative FE-SEM image of the nanowire channel region. The channel length and diameter of the representative device were  $\sim$ 2  $\mu$ m and 60 nm respectively.

# 2.3. Functionalization and characterization of ZTO NWTs

We performed two types of  $N_2$  plasma treatments for the fabricated devices. Regarding the conditions of the  $N_2$  plasma treatment, the  $N_2$  flow rate was divided into two different conditions—20 and 40 sccm—but the remaining conditions remained consistent at a bias power of 50 W, pressure of 200 mTorr, and exposure time of 60 s. In order to analyze the results, the 1/f noise characteristics of the as-fabricated and the plasma-treated devices were measured using a SR 570 low-noise current pre-amplifier and a HP 3561A dynamic signal analyzer.

## 3. Results and discussion

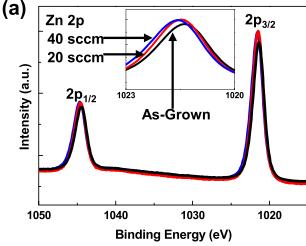

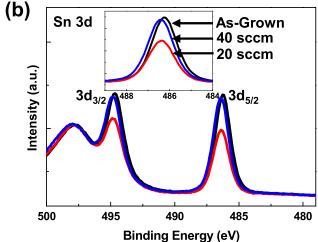

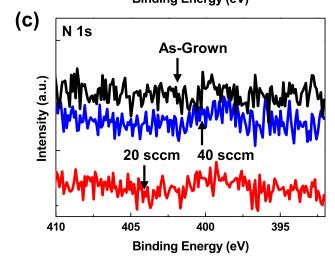

X-ray photoelectron spectroscopy (XPS) was employed to observe the chemical structure of the ZTO nanowires before and after N2 plasma treatment with varied N2 gas flow rate of 20 and 40 sccm. Figure 2 shows the Zn 2p, Sn 3d and N 1s core-level spectra of ZTO nanowires before and after N<sub>2</sub> plasma treatment (20 and 40 sccm). As shown in figure 2(a), the binding energies of Zn  $2p_{1/2}$  and Zn  $2p_{3/2}$  were observed at 1044.58 and 1021.38 eV prior to  $N_2$  plasma treatment. Following N<sub>2</sub> plasma treatment, the binding energies of Zn 2p<sub>1/2</sub> and Zn 2p<sub>3/2</sub> exhibit slight shifts towards the higher energy level by  $\sim$ 0.1 eV (20 sccm) and  $\sim$ 0.2 eV (40 sccm), respectively. Such slight shifts in binding energies can be attributed to the change of surface states and the increased number of oxygen vacancies at the nanowire surface which is also consistent with previous literature [29, 30]. The binding energies of Sn 3d<sub>3/2</sub> and Sn 3d<sub>5/2</sub> peaks were seen at 494.68

**Figure 2.** XPS profile for (a) Zn 2p peaks, (b) Sn 3d peaks, and (c) N 1s peaks of ZTO nanowires before and after  $N_2$  plasma treatment (20 and 40 sccm).

and 486.28 eV before  $N_2$  plasma treatment (figure 2(b)). As shown in the inset of figure 2(b), after  $N_2$  plasma treatment, the binding energies of Sn  $3d_{3/2}$  and Sn  $3d_{5/2}$  peaks showed slight shifts towards higher energy level by  $\sim 0.1$  eV (Sn  $3d_{5/2}$ ) and  $\sim 0.2$  eV (Sn  $3d_{3/2}$ ) [31, 32]. On the other hand, the fine spectra of N 1s did not show any distinct peaks over

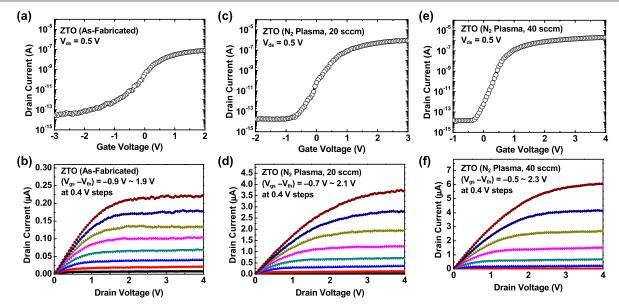

**Figure 3.**  $I_{ds}$ – $V_{gs}$  characteristics and  $I_{ds}$ – $V_{ds}$  characteristics of ZTO NWTs ((a), (b)) before and after N<sub>2</sub> plasma treatments with different N<sub>2</sub> flow rates of ((c), (d)) 20 sccm and ((e), (f)) 40 sccm.

the range even after  $N_2$  plasma treatment (figure 2(c)). The absence of nitrogen shown from the XPS data indicates that there is no significant chemical bonding between the ZTO nanowires and the nitrogen ions generated by the plasma. The atomic percentage of Sn to the total amount of Zn and Sn (Sn/(Sn+Zn)) obtained by the XPS is approximately 22.4%.

Figure 3 shows the drain current versus gate-source voltage  $(I_{ds}-V_{gs})$  and the drain current versus drain-source voltage  $(I_{ds}-V_{ds})$  characteristics of the ZTO NWTs before and after the N2 plasma treatment with different N2 flow rate of 20 and 40 sccm, respectively. In all cases, the ZTO NWTs exhibit typical characteristics of n-channel transistors. The  $I_{ds}$ – $V_{gs}$  curve of the as-fabricated ZTO NWT at  $V_{\rm ds} = 0.5$  V (as-fabricated) is shown in figure 3(a). The representative device exhibits  $V_{\text{th}}$  ( $V_{\text{gs}}$  at  $I_{\text{ds}} = 1$  nA) of 0.1 V, SS of 0.29 V/dec,  $\mu_{eff}$  of 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and  $I_{\rm on}/I_{\rm off}$  of 4.8  $\times$  10<sup>6</sup>. Here,  $\mu_{\rm eff}$  was extracted using the MOSFET model at small  $V_{\rm ds} \, (\mu_{\rm eff} = ({\rm d}I_{\rm ds}/{\rm d}V_{\rm gs}) \, imes$  $L_{\rm ch}^2/C_i/V_{\rm ds}$ ), where  $L_{\rm ch}\sim 2~\mu{\rm m}$  is the channel length, and  $C_i$  is the gate-to-channel capacitance. The gate-to-channel capacitance is determined from the cylinder-on-plate model  $(C_i = 2\pi \varepsilon_0 k_{\rm eff}/\cosh^{-1}(1 + t_{\rm ox}/r_{\rm nw}))$ , where  $k_{\rm eff} \sim 9$  is the effective dielectric constant of Al<sub>2</sub>O<sub>3</sub>;  $t_{ox} \sim 30$  nm, oxide thickness; and  $r_{\rm nw} \sim 30$  nm, the nanowire radius. Figure 3(b) shows the  $I_{ds}$ - $V_{ds}$  curve of the as-fabricated ZTO NWT. The on-current  $(I_{on})$  of the device is 0.19  $\mu$ A  $(V_{ds} = 4 \text{ V})$ and  $(V_{\rm gs}-V_{\rm th})=1.9$  V). For the ZTO NWTs exposed to N<sub>2</sub> plasma with N<sub>2</sub> gas flow rate of 20 sccm, positively shifted  $V_{\rm th}=0.3$  V, reduced SS = 0.21 V/dec, increased  $\mu_{\rm eff}=79~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$ , improved  $I_{\rm on}/I_{\rm off}=5.9\times10^7$ , and increased  $I_{\rm on}=3.7~\mu{\rm A}~(V_{\rm ds}=4~{\rm V}~{\rm and}~(V_{\rm gs}-V_{\rm th})=2.1~{\rm V})$  are obtained from the  $I_{ds}$ – $V_{gs}$  and  $I_{ds}$ – $V_{ds}$  curves (figures 3(c) and (d)), respectively. Figures 3(e) and (f) show the  $I_{ds}-V_{gs}$  and  $I_{\rm ds}$ - $V_{\rm ds}$  characteristics of the ZTO NWTs after the N<sub>2</sub> plasma treatment with the flow rate of 40 sccm. In this case, the device performance metrics further improve to  $V_{\rm th} = 0.5$  V, SS =

0.12 V/dec,  $\mu_{\rm eff} = 112 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ,  $I_{\rm on}/I_{\rm off} = 1.2 \times 10^8$ , and  $I_{\rm on} = 4.1 \ \mu \text{A}$  ( $V_{\rm ds} = 4 \text{ V}$  and ( $V_{\rm gs}-V_{\rm th}$ ) = 1.9 V). Note that the performance characteristics of ZTO NWTs following N<sub>2</sub> plasma treatment did not show significant changes under repeated measurement for seven days at room temperature in ambient air. In summary, upon N<sub>2</sub> plasma treatment with increased N<sub>2</sub> gas flow rate from 20 to 40 sccm, the device performance metrics of ZTO NWTs were improved in terms of SS,  $\mu_{\rm eff}$ ,  $I_{\rm on}/I_{\rm off}$ ,  $I_{\rm on}$ , along with positive shift in  $V_{\rm th}$ .

In order to investigate the effect of  $N_2$  plasma treatment on the interface quality of ZTO NWTs, the 1/f noise was measured for ZTO NWTs before and after the  $N_2$  plasma treatment with different  $N_2$  flow rates of 20 and 40 sccm. According to Hooge's empirical model, low-frequency noise is often characterized by the relationship

$$\frac{S_I}{I_{\rm ds}^2} = \frac{A}{f^{\eta}} = \frac{\alpha_{\rm H}}{N f^{\eta}} \tag{1}$$

where  $S_I$  is the drain current noise spectrum;  $I_{\rm ds}$ , the drain current; A, the noise amplitude;  $\alpha_{\rm H}$ , Hooge parameter; N, the total number of carriers in the nanowire channel; f, the frequency; and  $\eta$ , the frequency exponent (ideally 1) [25, 26]. In the device on-region, where  $V_{\rm gs} > V_{\rm th}$ , the equilibrium charge in the channel can be re-written as

$$Q = qN = C_i |V_{gs} - V_{th}| \tag{2}$$

where q is the electronic charge. Combining equations (1) and (2), the current noise spectrum from the channel at the on-region can be expressed as

$$\frac{S_I}{I_{\rm ds}^2} = \frac{q\alpha_{\rm H}}{f^{\eta}C_i}|V_{\rm gs} - V_{\rm th}|^{-1} = \beta|V_{\rm gs} - V_{\rm th}|^{-1}$$

(3)

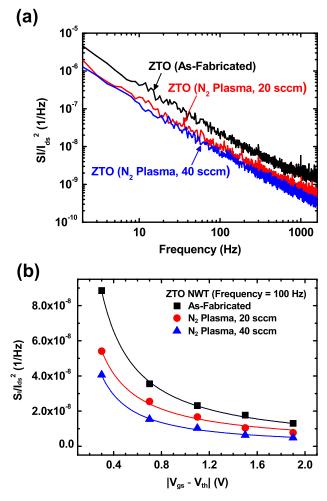

where  $\beta = q\alpha_{\rm H}f^{-\eta}C_i^{-1}$ . Figure 4(a) shows the normalized current noise spectral density  $(S_I/I_{\rm ds}^2)$  versus frequency (ranging from 1 Hz to 1.6 kHz) plot of ZTO NWTs prior to

**Figure 4.** (a) Normalized drain current noise spectrum  $(S_I/I_{\rm ds}^2)$  (at  $(V_{\rm gs}-V_{\rm th})=1.5~\rm V$ ) versus frequency and (b)  $S_I/I_{\rm ds}^2$  (at 100 Hz) versus  $(V_{\rm gs}-V_{\rm th})$  of ZTO NWTs before and after  $N_2$  plasma treatments with different  $N_2$  flow rates (20 and 40 sccm). The solid curves shown in (b) are the non-linear curve fits to each data points (symbol).

and following N<sub>2</sub> plasma treatment at  $(V_{\rm gs}-V_{\rm th})=1.5~\rm V$ . The frequency exponent  $\eta$  is obtained as 0.96–0.99, i.e., close to unity, from the linear fit of the spectrum. Note that  $\eta$  being approximately unity indicates that slow and fast traps are evenly distributed [33]. As shown in figure 4(a),  $S_I/I_{\rm ds}^2$  of the ZTO NWTs following N<sub>2</sub> plasma treatment with flow rates of 40 sccm (20 sccm) are reduced by 65% (41%) from that of the as-fabricated ZTO NWTs, respectively.

The 1/f noise in nanowire/nanotube-based transistors, which generally utilize metal source—drain electrodes similar to SB-FETs, may stem from (i) the excess noise in the metal–semiconductor Schottky barrier accompanying the generation–recombination noise in the space charge region, and/or (ii) electron trapping—detrapping events at the channel-to-dielectric interface, leading to carrier number fluctuations in the channel [12, 34]. In order to investigate the source of the noise in the fabricated ZTO NWTs, the current noise spectrum normalized by the drain current  $(S_I/I_{\rm ds}^2)$  versus  $(V_{\rm gs}-V_{\rm th})$  for ZTO NWTs before and after N<sub>2</sub> plasma treatment is plotted in figure 4(b). Note that

the measured  $S_I/I_{

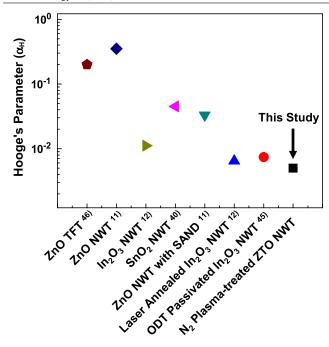

m ds}^2$  decreases non-linearly under the given range of  $(V_{\rm gs}-V_{\rm th})$  for all cases. From the curve fitting of  $S_I/I_{\rm ds}^2 = \beta (V_{\rm gs} - V_{\rm th})^m$  (solid curves) for each case (symbol), m values of -1.04 and -1.12 (-0.96) are obtained for ZTO NWTs before and after N<sub>2</sub> plasma treatment with flow rate of 40 (20) sccm, respectively. Such proportionality (m near -1) between  $S_I/I_{ds}^2$  and  $(V_{gs}-V_{th})$  has often been observed in FETs using carbon nanotubes and SnO2 nanowires as the channel material [11, 27]. In studies of 1/f noise in the on-region of ZnO NWTs, m = -1 behavior is observed at low  $(V_{gs}-V_{th})$  values, but m=0 is observed when  $(V_{gs}-V_{th})$  is very high (extreme on-region) [35]. It has also been reported that  $S_I/I_{ds}^2$  in MODFETs and InAs NWTs exhibits different  $V_{gs}^m$  dependences (m values of -1, -3, 0, and +2) depending on whether the contacts or channel dominate the noise and resistance, where m equals -1 (0) when the channel (contact) dominates both noise and resistance [36, 37]. As the  $S_I/I_{\rm ds}^2$ in our ZTO NWTs show m = -1 behavior with no sign of a m = 0 region, the channel appears to dominate both the noise and resistance throughout the measured  $V_{\rm gs}$  range. Furthermore, the low-field channel conductance ( $G_{ch}$ ), which is directly measured from the slope of  $I_{ds}$ – $V_{ds}$  curves (figure 3) at low  $V_{\rm ds}$ , increases approximately linearly with  $V_{\rm gs}$  from  $V_{\rm th}$  without saturation due to contact resistance  $(R_{\rm sb})$  limit, indicating that the channel resistance is dominating the overall resistance in the measured  $V_{\rm gs}$  range. Note that  $\alpha_{\rm H}$  can be extracted from equation (3) and the  $\beta$  values extracted from the non-linear fitting in figure 4(b). For the as-fabricated ZTO NWT,  $\alpha_{\rm H}$  is calculated as  $1.20 \times 10^{-2}$  where  $\beta =$  $2.53 \times 10^{-8}$ . Following N<sub>2</sub> plasma treatment of ZTO NWTs with  $N_2$  flow rates of 20 sccm and 40 sccm, lower  $\alpha_H$  of  $8.14 \times 10^{-3} \ (\beta = 1.71 \times 10^{-8}) \ \text{and} \ 4.99 \times 10^{-3} \ (\beta = 1.71 \times 10^{-8})$  $1.05 \times 10^{-8}$ ) are estimated, respectively. Hooge parameter  $\alpha_{\rm H}$  is often used as a figure-of-merit to compare the 1/fnoise in different devices regardless of the measurement ambient and material which gives important information about the interface trap densities. The reduction of  $\alpha_H$ upon N<sub>2</sub> plasma treatment indicates that the interface traps are reduced at the nanowire channel [11, 12, 40, 45]. Although the nanowires exhibit high surface-to-volume ratios,  $\alpha_H$  value obtained from the  $N_2$  plasma-treated ZTO NWTs (40 sccm) are comparable to or lower than that of the CMOS FETs developed using metal gate and high-k gate dielectric [38, 39]. Furthermore, the  $\alpha_{\rm H} \sim 4.99 \times 10^{-3}$ for ZTO NWT is among the lowest value reported in oxide-based TFTs and NWTs as shown in figure 5. Note that the  $\alpha_H$  obtained from the  $N_2$  plasma-treated ZTO NWT (40 sccm) is nearly one order of magnitude lower than the previously reported Hooge's parameter values extracted from oxide-based (ZnO, In<sub>2</sub>O<sub>3</sub>, and SnO<sub>2</sub>) NWTs [11, 12, 40]. Although our measurements were performed in air, the  $\alpha_{\rm H}$  ~  $4.99 \times 10^{-3}$  for ZTO NWT is comparable to the value previously reported for ZnO NWTs measured in ultrahigh vacuum; 2-4 times higher values are typically observed for measurements in oxygen ambient [35].

The decrease in  $S_I/I_{\rm ds}^2$  (and  $\alpha_{\rm H}$ ) and improvement of the device performance upon N<sub>2</sub> plasma treatment is known to be attributed to the decrease of interface trap density and

**Figure 5.** Hooge's parameters of various oxide-based TFTs and NWTs.

the reduction of surface scattering at the nanowire channel region [36, 37]. Note that as the plasma treatment is performed after the source–drain metallization, the metal-to-nanowire contact is expected to be shielded from the effects of the plasma, although the band-bending near the contacts may change. It has been reported in previous literature that plasma treatment removes surface organic layers and contaminants, increasing the adhesion between layers and improving the interface quality [41, 42]. To investigate the shift in the interface trap densities ( $Q_{\rm IT}$ ) upon N<sub>2</sub> plasma treatment, we calculated the  $Q_{\rm IT}$  from the measured 1/f noise amplitude and SS. When carrier number fluctuation is the dominant mechanism in 1/f noise,  $S_I/I_{\rm ds}^2$  can be expressed as

$$\frac{S_I}{I_{dc}^2} = \frac{kT}{f\gamma N^2 r_{\rm nw} L_{\rm ch}} N_{\rm IT}(E_{\rm F}) \tag{4}$$

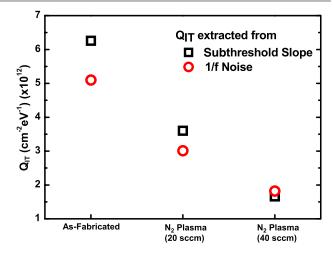

from the unified model for flicker noise reported by Hung et~al~[43]. Here, k is the Boltzmann constant, T the temperature,  $N_{\rm IT}(E_{\rm F})$  the interface trap density at the Fermi level  $(E_{\rm F})$  (in units of cm<sup>-3</sup> eV<sup>-1</sup>), and  $\gamma = 4\pi\sqrt{2m^*\Phi_{\rm TB}}/h$  the attenuation coefficient of the electron wavefunction in the oxide where h is the Planck's constant,  $m^*$  is the effective mass of the carrier in oxide, and  $\Phi_{\rm TB}$  is the tunneling barrier height seen by the carriers at the interface [43]. From equation (4) and  $S_I/I_{\rm ds}^2$  values  $(f=100~{\rm Hz})$  at fixed  $(V_{\rm gs}-V_{\rm th})=1.5~{\rm V}, Q_{\rm IT}$  values of  $5.10\times10^{12}~{\rm cm}^{-2}~{\rm eV}^{-1}$  and  $1.82\times10^{12}~{\rm cm}^2~{\rm eV}^{-1}$  (3.01×10<sup>12</sup> cm<sup>-12</sup> eV<sup>-1</sup>) are extracted for as-fabricated and 40 sccm (20 sccm) N<sub>2</sub>-plasma-treated ZTO NWTs, respectively (figure 6).

While 1/f noise is well known to provide information about the  $Q_{\rm IT}$  near the Fermi level, SS is more related to the  $Q_{\rm IT}$  in the subthreshold region [43]. The SS can be calculated

**Figure 6.** The interface trap density  $(Q_{\rm IT})$  values extracted from the SS and 1/f noise spectrum (at 100 Hz) are shown for ZTO NWTs before and after N<sub>2</sub> plasma treatment with different N<sub>2</sub> flow rates (20 and 40 sccm).

from the equation [44]

SS =

$$(\ln 10) \left(\frac{kT}{q}\right) \left(1 + \frac{C_{\text{dep}} + C_{\text{IT}}}{C_{\text{ox}}}\right).$$

(5)

In fully depleted nanowires,  $C_{\text{dep}}$ , the depletion-layer capacitance is negligible, while  $C_{\rm IT} = q^2 Q_{\rm IT}$ , the interface trap capacitance, and  $C_{ox}$ , the oxide capacitance (in units of F cm $^{-2}$ ), play a major role in determining the SS values. From equation (5) and the measured SS values,  $Q_{\rm IT}$  of  $5.10\times10^{12}~{\rm cm^{-2}~eV^{-1}}$  and  $1.82\times10^{12}~{\rm cm^{-2}~eV^{-1}}$  (3.01  $\times$  10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup>) are estimated for as-fabricated and 40 (20) sccm N<sub>2</sub> plasma-treated devices, respectively (figure 6). We have reported that in the case of back-gated devices where the cylindrical nanowires are placed on top of a large plane of gate dielectric, the  $Q_{\rm IT}$  extracted from 1/f noise spectrum is closely related to the traps located at the nanowire-to-dielectric interface, while  $Q_{\rm IT}$  from SS is more related to the quality of the nanowire surface exposed to ambient [45]. Note that the  $Q_{\rm IT}$  values extracted from both 1/f noise and SS decreased upon  $N_2$  plasma treatment with increased N2 gas flow rate, indicating that the decreased SS, lowered noise power and lowered  $\alpha_H$  upon plasma treatment is presumably related to the improvement in the quality of the nanowire surface as well as the interface at the nanowire-to-dielectric. Therefore, the decreased  $Q_{\rm IT}$ upon plasma treatment is expected to reduce the surface scattering and improve the ZTO NWT performance in terms of SS,  $\mu_{\rm eff}$ ,  $I_{\rm on}$ ,  $I_{\rm on}/I_{\rm off}$  and  $V_{\rm th}$ . Also, the slight increase of oxygen vacancies, donor-like traps, after N2 plasma exposure (evidenced from the XPS data) further increases the conductivity of the nanowire and hence increases  $I_{\text{on}}$  [3, 14, 45].

#### 4. Conclusions

In summary, the interface quality of high-performance ZTO NWTs after the N<sub>2</sub> plasma treatment was investigated by the

current–voltage characteristics and 1/f noise as a function of gate bias. The  $N_2$  plasma treatment was employed in order to reduce the interface state densities, to improve the device performance metrics in terms of SS,  $\mu_{\rm eff}$ ,  $I_{\rm on}/I_{\rm off}$ , and  $I_{\rm on}$ , and to achieve low-noise densities. The  $S_I/I_{\rm ds}^2$  values of the  $N_2$  plasma-treated ZTO NWTs with  $N_2$  flow rates of 20 and 40 sccm were 41% and 65% less than that of as-fabricated ZTO NWTs. The low  $\alpha_{\rm H}$  value of  $\sim$ 4.99  $\times$  10<sup>-3</sup> for the  $N_2$  plasma-treated (40 sccm) ZTO NWTs indicated that the ZTO nanowire interface had higher quality than the as-fabricated ZTO nanowire interface. These results suggest opportunities for the fabrication of robust and high-quality ZTO NWTs that can be applied to low-power, high-performance, and low-noise nano-electronic devices.

# Acknowledgments

We thank C J Delker at Purdue University for discussions on 1/f noise physics. This research was partially supported by the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (2012K001317 and 2012R1A2A2A01013734), and also supported by the National Science Foundation (ECCS-1118934 and ECCS-1202281).

#### References

- [1] Cui Y and Lieber C M 2001 Science 291 851

- [2] Hochbaum A I, Chen R, Delgado R D, Liang W, Garnett E C, Najarian M, Majumdar A and Yang P 2008 Nature 451 163

- [3] Ju S, Facchetti A, Xuan Y, Liu J, Ishikawa F, Ye P, Zhou C, Marks T J and Janes D B 2007 Nature Nanotechnol. 2 378

- [4] Kolmakov A, Zhang Y, Cheng G and Moskovits M 2003 Adv. Mater. 15 997

- [5] Park W I, Kim J S, Yi G-C and Lee H-J 2005 Adv. Mater. 17 1393

- [6] Ju S et al 2008 Nano Lett. 8 997

- [7] Dattoli E N, Wan Q, Guo W, Chen Y, Pan X and Lu W 2007 Nano Lett. 8 2463

- [8] Ju S, Ishikawa F, Chen P, Chang H-K, Zhou C, Ha Y, Liu J, Facchetti A, Marks T J and Janes D B 2008 Appl. Phys. Lett. 92 222105

- [9] Lim T, Kim H, Meyyappan M and Ju S 2012 ACS Nano 6 4912

- [10] Zhuge J, Wang R, Hunag R, Tian Y, Zhang L, Kim D-W, Park D and Wang Y 2009 IEEE Electron Device Lett. 30 57

- [11] Ju S, Kim S, Mohammadi S, Janes D B, Ha Y-G, Facchetti A and Marks T 2008 J. Appl. Phys. Lett. 92 022104

- [12] Kim S et al 2011 J. Phys. Chem. C 115 17147

- [13] Wang J, Polizzi E, Ghosh A, Datta S and Lundstrom M 2005 Appl. Phys. Lett. 87 043101

- [14] Kim S, Delker C, Chen P, Zhou C, Ju S and Janes D B 2010 Nanotechnology 21 145207

- [15] Kim S, Lim T and Ju S 2011 *Nanotechnology* **22** 305704

- [16] Law J B K and Thong J T L 2008 Nanotechnology 19 205502

- [17] Greene L E, Law M, Goldberger J, Kim F, Johnson J C, Zhang Y, Saykally R J and Yang P 2003 Angew. Chem. Int. Edn 42 3031

- [18] Wan Q, Dattoli E N and Lu W 2007 Appl. Phys. Lett. 90 222107

- [19] Chen P-C et al 2009 ACS Nano 3 3383

- [20] Shen Y, Yamazaki T, Liu Z, Meng D, Kikuta T, Nakatani N, Saito M and Mori M 2009 Sensors Actuators B 135 524

- [21] He H Jr, Lao C S, Chen L J, Davidovic D and Wang Z L 2005 J. Am. Chem. Soc. 127 16376

- [22] Bae S Y, Na C W, Kang J H and Park J 2005 J. Phys. Chem. B 109 2526

- [23] Li S Y, Lin P, Lee C Y, Tseng T Y and Huang C J 2004 J. Phys. D: Appl. Phys. 37 2274

- [24] Bid A, Bora A and Raychaudhuri A K 2006 Nanotechnology 17 152

- [25] Scholten A J, Tiemeijer L F, van Langevelde R, Havens R J, Zegers-van Duijnhoven A T A and Venezia V C 2003 IEEE Trans. Eelectron Devices 50 618

- [26] Rumyantsev S L, Shur M S, Levinshtein M E, Motayed A and Davydov A V 2008 J. Appl. Phys. 103 064501

- [27] Ishigami M, Chen J H, Williams E D, Tobias D, Chen Y F and Fuhrer M S 2006 Appl. Phys. Lett. 88 203116

- [28] Fan Z, Wang D, Chang P, Tseng W and Lu J G 2004 Appl. Phys. Lett. 85 5923

- [29] Remashan K, Hwang D K, Park S D, Bae J W, Yeom G Y, Park S J and Janga J H 2008 Electrochem. Solid-State Lett. 11 H55

- [30] Zhang Y, Du G, Wang X, Li W, Yang X, Ma Y, Zhao B, Yang H, Liu D and Yang S 2003 J. Cryst. Growth 252 180

- [31] Jing L, Fu H, Wang B, Wang D, Xin B, Li S and Sun J 2006 Appl. Catal. B 62 282

- [32] Themlin J-M, Chtaib M, Henrard L, Lambin P, Darville J and Gilles J-M 1992 *Phys. Rev.* B **46** 2460

- [33] von Haartman M and Östling M 2007 Low-Frequency Noise in Advanced MOS Devices (New York: Springer)

- [34] Kim S, Kim S, Janes D B, Mohammadi S, Baek J and Shim M 2010 *Nanotechnology* **21** 385203

- [35] Wang W, Xiong H D, Edelstein M D, Gundlach D, Suehle H S, Richter C A, Hong W K and Lee T 2007 J. Appl. Phys. 101 044313

- [36] Vandamme L K J 1994 IEEE Trans. Electron Devices 41 2176

- [37] Delker C, Kim S, Borg M, Wernersson L and Janes D B 2012 IEEE Trans. Electron Devices 59 1980

- [38] Claeys C, Simoen E, Mercha A, Pantisano L and Young E 2005 J. Electrochem. Soc. 152 F115

- [39] Min B, Devireddy S P, Çelik-Butler Z, Wang F, Zlotnicka A, Tseng H-H and Tobin P J 2004 IEEE Trans. Electron Devices 51 1315

- [40] Ju S, Chen P, Zhou C, Ha Y-G, Facchetti A, Marks T J, Kim S, Mohammadi S and Janes D B 2008 Appl. Phys. Lett. 92 243120

- [41] Shenton M J and Stevens G C 2001 J. Phys. D: Appl. Phys. 34 2761

- [42] Shenton M J, Lovell-Hoare M C and Stevens G C 2001 J. Phys. D: Appl. Phys. 34 2754

- [43] Hung K K, Ko P K, Hu C and Cheng Y C 1990 *IEEE Trans. Electron Devices* **37** 654

- [44] Sze S M and Ng K K 2007 *Physics of Semiconductor Devices* 3rd edn (Hoboken, NJ: Wiley)

- [45] Kim S, Carpenter P D, Jean R K, Chen H, Zhou C, Ju S and Janes D B 2012 ACS Nano 6 7352

- [46] Jeong K S, Kim Y M, Park J G, Yang S D, Kim Y S and Lee G W 2011 AIP Conf. Proc. 1399 891