# **Purdue University** Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

6-2013

# Transconductance Linearity Analysis of 1-D, Nanowire FETs in the Quantum Capacitance Limit

Ali Razavieh

Birck Nanotechnology Center, Purdue University, arazavie@purdue.edu

David B. Janes

Birck Nanotechnology Center, Purdue University, janes@purdue.edu

Joerg Appenzeller

Birck Nanotechnology Center, Purdue University, appenzeller@purdue.edu

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub

Part of the Nanoscience and Nanotechnology Commons

Razavieh, Ali; Janes, David B.; and Appenzeller, Joerg, "Transconductance Linearity Analysis of 1-D, Nanowire FETs in the Quantum Capacitance Limit" (2013). Birck and NCN Publications. Paper 1403. http://dx.doi.org/10.1109/TED.2013.2259238

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# Transconductance Linearity Analysis of 1-D, Nanowire FETs in the Quantum Capacitance Limit

Ali Razavieh, David B. Janes, Member, IEEE, and Joerg Appenzeller, Fellow, IEEE

Abstract—The impact of channel material and dimensionality on the linearity of nanowire transistors is studied theoretically. This paper also evaluates various scattering mechanisms in this context. While operating under 1-D transport conditions in the quantum capacitance limit, the achievable device linearity strongly depends on the details of the scattering mechanisms limiting the transport. Interestingly, it is not only the scattering length that determines the third-order intercept point but also the particular energy dependence of the dominant-scattering mechanism that needs to be considered. Our results provide critical insights for the choice of material to obtain the desired device linearity.

Index Terms—1-D transport, ballistic transport, nanowire transistor, quantum capacitance, RF linearity, scattering, transconductance.

#### I. INTRODUCTION

SILICON has proved to be an outstanding candidate for both digital and analog applications. However, in both fields, competing technologies are explored to outperform existing silicon-based device and circuit solutions. For applications, such as multifunctional and reconfigurable wireless communication systems, GPS systems, and WLAN, high linearity is a key requirement for: 1) RF front end of receivers to prevent intermodulation and harmonic distortion and 2) increasing the output power of the transmitters in order to obtain high-performance RF transceivers.

Over the years, many circuit design techniques have been developed to improve RF linearity in integrated circuits [1]–[5]. Although these methods are well established, they are usually complex, and trade off linearity with power consumption. In the last decade, device engineers have been trying to understand and improve RF linearity at the device level [6]–[12] in order to reduce the complexity and high power consumption of circuit-level linearization techniques. These works have mainly focused on conventional MOSFETs, SOI MOSFETs, and HEMTs, which are commercially available RF transistors, and thus far, there has been no effort to analyze the linearity in low-dimensional devices such as nanowire FETs. Theoretical studies show that devices from low-dimensional

Manuscript received October 22, 2012; revised April 16, 2013; accepted April 16, 2013. Date of current version May 16, 2013. The review of this paper was arranged by Editor R. K. Lake.

The authors are with the Department of Electrical and Computer Engineering, Birck Nanotechnology Center, Purdue University, West Lafayette, IN USA 47907 (e-mail: arazavie@purdue.edu; janes@ecn.purdue.edu; appenzeller@purdue.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2013.2259238

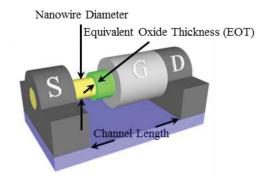

Fig. 1. Schematic illustration of a gate-all-around nanowire FET. In reality gate metal contact and the gate dielectric wrap the entire channel.

materials, such as nanowires and carbon nanotubes, can intrinsically provide an ideal linear  $I_d - V_{\rm gs}$  characteristic under the right conditions [13], [14]. In the case of nanowire devices, one can show that

$$I_D = \frac{2q^2}{h}(V_{GS} - V_{th}) \tag{1}$$

if three conditions: 1) 1-D transport, 2) operation in the quantum capacitance limit (QCL), and 3) ballistic transport are satisfied simultaneously and drain voltages are sufficiently high to allow operation in the saturation region of the output characteristics without the introduction of the scattering [13]–[16].

Recently, we have experimentally explored the potential of this category of devices for RF applications when high linearity is a key factor. A theoretically predicted constant transconductance of  $2q^2/h = 77.6 \mu S$  over a wide input voltage range promises a high degree of RF linearity with very low supply voltage requirements if devices show negligible variations in their output conductances [15]. We have also discussed how the characteristics of these devices can be interpreted in terms of their RF linearity performance if the above transport criteria cannot be ideally met. In particular, the effect of transitioning from diffusive transport to quasi-ballistic and ballistic transport on RF linearity has been examined for silicon nanowires [16].

The main focus of this paper is to provide a set of guidelines for material parameters and device dimensions for nanowire field-effect transistors (FETs)—see Fig. 1—that meet the above-mentioned three criteria. In addition, we discuss limitations of fulfilling any of the above transport conditions from a material's point of view. The analysis also considers the energy dependence of scattering mechanisms that are expected

to be significant in the case of 1-D nanowire transistors, and evaluates the degree of RF linearity that can be obtained for a given scattering mechanism. Although, circuit topology in general affects the linearity performance of transistors, this paper focuses on transconductance linearity, which is expected to have an impact on circuit linearity regardless of circuit topology.

### II. QUANTUM CAPACITANCE LIMIT

This section considers the materials and geometry parameters, including required dielectric thickness, needed for operation of the device in the QCL. When coupled with the requirement for operation in single 1-D sub-band (see Section III), an overall set of parameters required for simultaneous operation in 1-D and the QCL limit can be obtained.

The channel region of a floating-body metal-oxide-semiconductor FET (MOSFET) can be regarded as a capacitor-based voltage divider (see inset of Fig. 2), in which gate voltage and channel potential  $\Phi_f$  are related through

$$d\Phi_f = \frac{qC_{OX}}{C_{OX} + C_O} dV_{GS}.$$

(2)

$C_{\rm OX}$  indicates the constant gate-oxide capacitance, and is determined by the geometry of the device. For the calculations in this section,  $C_{\rm OX}$  is considered to be a coaxial cylindrical capacitor for simplicity.  $C_{\rm Q}$  is the gate-voltage-dependent inversion layer capacitance, or the so-called quantum capacitance, which is significant in low-dimensional transistors [17], [18].  $C_{\rm Q}$  is given by

$$C_Q = -q \int dE \cdot \text{DOS}_{1\text{-D}}(E) \frac{\partial \left(E - E_f^S\right)}{\partial E}.$$

(3)

Measurements have shown that  $C_Q$  is a variable capacitor and follows the trend of the DOS(E) [19]. According to the relative magnitudes of  $C_{OX}$  and  $C_Q$ , all transistors can be divided into the following categories.

$$A. C_O >> C_{OX}$$

In this regime, the transistor operates in the chargecontrolled or classical limit, i.e. the channel charge is proportional to the electric field in the gate oxide (above threshold). Thus,  $d\Phi_f/dV_{gs} \rightarrow 0$  in the on-state [see (2)] and energy bands don't move or move very slowly due the substantial voltage drop across the gate dielectric. In this case, linear  $I_{\rm d}-V_{\rm GS}$  characteristics can be obtained only if the velocity of the charge carriers inside the channel does not depend on the gate voltage. Two scenarios can create this situation: 1) scattering results in velocity saturation. Under this condition, the material choice and the details of scattering need to be considered, and the potential of this approach for the desired linearity discussed here is somewhat questionable. In addition, high drain fields may be needed to enable velocity saturation and 2) ballistic transport results in a constant thermal velocity. Since this statement is only true for the nondegenerate case and, thus, low-carrier concentrations in the channel, in reality the carrier velocity keeps increasing with increasing carrier concentration and is thus gate voltage-dependent.

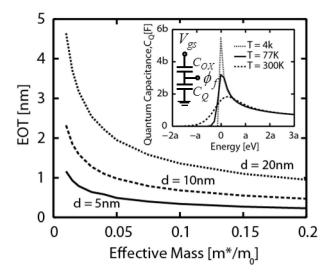

Fig. 2. EOT required for operation in the QCL versus bulk effective mass (e.g., Table. I) for three different wire diameters. A threshold of  $C_{\rm OX}=10C_{\rm Qmax}$  is defined as the onset of the QCL. Inset shows 1) the quantum capacitance for a 1-D single parabolic sub-band device, and 2) a simplified capacitance model for MOSFETs.

## B. $C_Q << C_{OX}$

In this regime, the QCL device operation is best described as band controlled, i.e., the change in channel charge due to a given change in gate voltage is related to the DOS at that bias point. In the QCL  $d\Phi_f/dV_{gs} \rightarrow 1$ —see (2)—the energy bands move approximately 1:1 with the gate voltage for voltages above the threshold. In this case, the electric field in the gate dielectric remains nearly constant. In the QCL, the ideal 1-D ballistic drain current will increase linearly with the gate voltage as pointed out above. This regime can be achieved in systems such as 1-D nanowire MOSFETs. Since the quantum capacitance is proportional to the density of states, C<sub>O</sub> follows the decreasing trend of DOS<sub>1-D</sub>(E) (see inset of Fig. 2) allowing C<sub>O</sub> to be smaller than C<sub>OX</sub> for realistic oxide thicknesses. Note that the effective mass is used in Fig. 2 only to calculate the DOS close to the band minimum where a parabolic approximation is justified to allow assessing  $C_{Omax}$ . Since  $C_{ox}$  is compared with  $C_{Omax}$ , the EOT value that can be extracted from Fig. 2 does not depend on the position of the Fermi level, and the effective mass approximation used here is adequate even for materials with small effective mass. Moreover, we note that our approach requires only very small drain and gate voltages, further justifying our approach.

Fig. 2 shows the required equivalent oxide thickness (EOT) as a function of effective mass (m\*) and diameter for operation in the QCL. In this paper  $C_{OX}=10C_{Qmax}$  is defined as the QCL to ensure minimal voltage drop across the oxide.  $C_{Qmax}$  is the maximum value of the quantum capacitance, which occurs at the band onset. Due to the energy dependence of  $C_Q$  (see inset of Fig. 2), the ratio between  $C_{OX}$  and  $C_Q$  will increase with increasing gate voltage beyond the bias corresponding to  $C_{Qmax}$ . It is apparent from Fig. 2 that for a particular wire diameter, materials with a smaller effective mass provide smaller  $C_{Qmax}$  and thus it is possible to satisfy the condition  $C_{OX}=10C_{Omax}$  at larger EOT values.

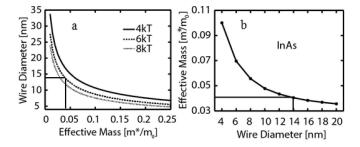

Fig. 3. (a) Required body thickness for a wide range of effective masses (e.g., Table. I, [20], [21]) for three different  $\Delta E$  values. (b) Calculated bottom of the band transport effective mass for InAs versus wire diameter; variation is due to band structure modifications introduced by quantum confinement.

On the other hand, for a particular channel material, increasing the wire diameter increases  $C_{OX}$ . Assuming that 1-D transport is still preserved (see discussion in Section III), the QCL condition can be satisfied for larger EOT thicknesses when the wire diameter is increased. Note that operation in both the 1-D regime and QCL requires simultaneously satisfying the relationships described in Figs. 1 and 2, i.e., for a given effective mass, one must choose the proper nanowire diameter (see Fig. 3) and then realize a suitable EOT for that diameter (see Fig. 2).

Section III will provide an example for a 1-D InAs channel with a  $\Delta E$  (mode spacing between the lowest sub-bands) of 6 kT, and we will show that a wire diameter of  $\sim$ 14 nm, which is associated with the transport effective mass of  $\sim$ 0.04 m<sub>0</sub>, is needed to achieve the targeted 1-D transport condition. Based on this information, one can extract a needed EOT of 1.5 nm from the plot in Fig. 2 for this device to achieve operation in the QCL indicating that for realistic geometries 1-D transport in the QCL can be achieved in materials such as InAs. For a particular channel material, the above procedure can be used to determine the diameter and EOT required for operation in the 1-D transport regime and the QCL.

# III. 1-D TRANSPORT

The unique scaling potential of nanowire FETs in terms of body thickness, oxide thickness, and channel length makes this class of devices particularly suitable for operation in the 1-D ballistic transport regime in the QCL. The significance of 1-D transport lies in two aspects: 1) the density of states (DOS) associated with a parabolic 1-D mode decreases with increasing energy which makes entering the QCL easier (see last section) and 2) since current calculation involves the product of DOS and group velocity within the Landauer formalism independent of the exact shape of the E(k) relation, the specific energy dependency of DOS and group velocity don't impact the linearity of the device. This is true since the product of DOS and group velocity is always a constant in the 1-D ballistic case. In the following, we will explain how the required body thickness (wire diameter) to satisfy room temperature 1-D transport for a specific channel material may in principle be determined if the mode spacing between the lowest subbands ( $\Delta E$ ) is known. As an example, this section also discusses how the required wire diameter for an InAs channel

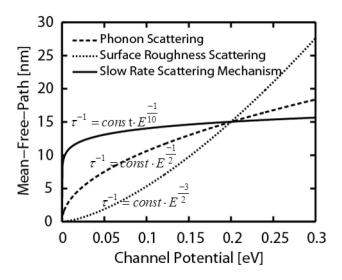

Fig. 4. Dependence of the mean-free-path  $[\lambda(E)]$  on energy for different scattering mechanisms. All curves are normalized to coincide at the same value of  $\lambda(E)$  at maximum channel potential for operation in the first subband (8 kT). Dashed lines correspond to cases for OPS (S=-1/2) and SRS (S=-3/2) in 1-D systems, and solid line corresponds to a small characteristic exponent of -1/10 for comparison purposes.

can be chosen to achieve  $\Delta E$  of 6 kT. In the simplest particle in a box approximation, one expects the 1-D mode spacing  $\Delta E$  in a nanowire to follow a  $(1/diameter)^2$  dependence and thus diameter  $\propto \sqrt{(1/m^*)}$  for constant  $\Delta E$ . Fig. 3(a) shows the calculated nanowire diameter required to achieve a subband spacing of 4, 6, or 8 kT at room temperature under this assumption and using bulk effective mass. Since the effective mass of a nanowire is itself dependent on the wire diameter due to confinement effects that result in a modification of the band structure [22]-[25], this approach only allows for a rough estimate. Fig. 3(b) shows the modified effective mass for the case of InAs nanowires, calculated using a tight binding approach including the aforementioned band structure change. Using the bulk effective mass  $(0.023m_0)$ , a  $\Delta E$  of 6kT would require a wire diameter of ~18 nm according to Fig. 3(a). Taking into account the modified band structure, a wire diameter of  $\sim$ 14 nm and a modified effective mass of  $\sim$ 0.04 m<sub>0</sub> is determined instead, illustrating the relevance of this effect for typical wire diameters.

#### IV. QUASI-BALLISTIC TRANSPORT

#### A. Quasi-Ballistic Current

As mentioned in the introduction, in addition to 1-D transport in the QCL, ballistic transport is a key requirement to achieve current linearity in low-dimensional transistors. In reality, ideal ballistic transport is challenging to achieve for practical channel lengths in today's leading semiconductor device technologies, including CMOS. This statement is true despite the fact that a low DOS in 1-D can facilitate a longer scattering mean-free-path because of the reduced phase space available for the scattering events. Thus, understanding the effect of carrier scattering on linearity in the quasi-ballistic regime is critical in order to determine the degree of linearity that can be achieved for practical devices.

The crystallographic structure of the channel plays a major role in determining the dominant scattering mechanism in a device [26], [27]. For example, in compound semiconductors such as InAs, polar optical phonon scattering (POP) is the dominant scattering mechanism in 3-D or 2-D channels, while in silicon, based on the strength of the electric field different scattering mechanisms, such as ionized impurity scattering (IIS), optical phonon scattering (OPS), or surface roughness scattering (SRS), can prevail in the channel [28]. To evaluate and compare the effect of different scattering mechanisms on device linearity, this section focuses on aggressively scaled silicon nanowire transistors with only one scattering mechanism present in the channel at a time. The effects of SRS, OPS, and an unspecified slow-rate scattering mechanism on current linearity in aggressively scaled silicon nanowire transistors as an example of channel material are discussed. As observed in the universal mobility model, operation at modest vertical electric fields in the on-state of the device corresponds to a condition where IIS can be disregarded [29], [30]. When a single 1-D sub-band is involved in carrier transport, M(E) = 1, the current in a quasi-ballistic channel in the QCL can be modeled using Landauer formalism [28], [31]

$$I_d = \frac{2q}{h} \int_0^{\varphi_f} T(E) \cdot M(E) \cdot [f_S(E) - f_D(E)] \cdot dE \qquad (4)$$

$$T(E) = \frac{\lambda(E)}{\lambda(E) + L_{\text{eff}}}.$$

(5)

In (4)  $\Phi_f$  is the maximum surface potential in the channel,  $f_{S,D}(E)$  represent source and drain Fermi distributions, T(E) is the transmission coefficient, which depends on the mean-free-path,  $\lambda(E)$ , and the channel length (L). Equation (6) shows how  $\lambda(E)$  can be calculated for different scattering mechanisms in a 1-D channel [32]

$$\langle \langle \lambda(E) \rangle \rangle = 2 \cdot v(E) \cdot \tau(E). \tag{6}$$

v(E) is the group velocity of the carriers, and can be directly extracted from the curvature of the band structure at each energy point. For silicon nanowire transistors operating in the saturation region, velocity can be approximated by the constant value of  $\sim 1.2 \times 10^7 \text{cm/s}$ .  $\tau(E)$  is the scattering time. For an analytical calculation of scattering effects, it is convenient to express the scattering rate in power law form [28]

$$\tau^{-1}(E) = \text{constant} \cdot E^{S}. \tag{7}$$

E denotes the energy of the particle relative to the conduction band minimum and S is the characteristic exponent which is different for each scattering mechanism. For SRS in silicon nanowire transistors, S can be extracted from the transport distribution function,  $\Xi(E)$ , and its relation to the thermoelectric coefficients derived from Linearized Boltzman theory.  $\Xi(E)$  for single parabolic band structures can be expressed as follows [33]:

$$\Xi(E) = DOS_{1D}(E) \cdot v^{2}(E) \cdot \tau(E). \tag{8}$$

For aggressively scaled silicon nanowire transistors,  $\Xi(E)$  exhibits a quadratic energy dependence for SRS [34].

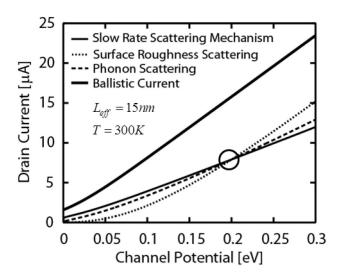

Fig. 5. Drain current versus channel potential for i) an ideal 1-D ballistic device operating in the QCL and ii) for 1-D quasi-ballistic devices in the QCL using mfpvs energy dependences presented in Fig. 4. Curves were calculated at  $V_{DS} = 1$  V.

Knowing the energy dependency of  $\Xi(E)$ ,  $DOS_{1-D}(E)$ , and v(E), the characteristic exponent for SRS can be extracted, as S = -3/2. The scattering rate for OPS is proportional to the  $DOS_{1-D}(E)$  resulting in a characteristic exponent of S = -1/2 [28]. Knowing the carriers' group velocity and scattering time, one can calculate the dependence of the mean-free-path (mfp) on energy (see Fig. 4) using (6). Note that the constant values in (6) are chosen such that the  $\lambda(E)$  values for all scattering mechanisms coincide at the same energy point of E = 200 meV.

Fig. 5 illustrates the resulting drain currents of 1-D quasiballistic devices in the QCL using (4), and the  $\lambda(E)$  values of Fig. 4. The current of an ideal 1-D ballistic device in the QCL is also plotted for comparison purposes. It is apparent from Figs. 4 and 5 that the quasi-ballistic currents all increase monotonically with channel potential due to the corresponding increase in the respective  $\lambda(E)$  relationships. As expected from normalization of  $\lambda(E)$ , all show the same current value at a channel potential of 200 meV. However, scattering mechanisms with different rate of change of mean-free-path versus energy result in different current linearity (as will be discussed below) if compared with the current of an ideal 1-D ballistic device in the QCL (see Fig. 5).

The following part explores the effect of carrier scattering on RF linearity, through third-order intercept point (IIP3) analysis.

#### B. RF Linearity

In telecommunications, IIP3 is a standard measure to evaluate the linearity performance of weakly nonlinear systems such as LNAs, mixers, and power amplifiers [7], [35]. It is assumed that transistors are biased to operate in the saturation regime of the  $I_{\rm D}-V_{\rm DS}$  characteristics. Unlike conventional MOSFETs, a strong dependence on the output conductance is ignored assuming good electrostatics control in nanowire

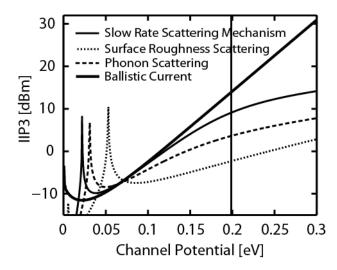

Fig. 6. IIP3 values for 1-D devices in the QCL considering different scattering mechanisms. See Fig. 4 for the related currents. IIP3 plot for an ideal ballistic channel is shown for comparison.

| TABLE I                  |       |      |

|--------------------------|-------|------|

| TRANSPORT EFFECTIVE MASS | [20], | [21] |

| channel material | BULK EFFECTIVE MASS[M*/M <sub>0</sub> ] |

|------------------|-----------------------------------------|

| InSb             | 0.0145                                  |

| InAs             | 0.023                                   |

| InGaAs           | 0.041                                   |

| GaSb             | 0.042                                   |

| GaAs             | 0.063                                   |

| InP              | 0.077                                   |

| Ge               | $0.082^{t}$                             |

| Si               | $0.19^{t}$                              |

| GaN              | 0.27                                    |

| ZnO              | 0.27                                    |

devices. In this case, the IIP3 is given by the following [6]:

IIP3 =

$$\frac{2g_{m1}}{3g_{m3}R_S} = \frac{4\left(\frac{\partial I_D}{\partial V_{gs}}\right)}{R_S\left(\frac{\partial^3 I_D}{\partial V_{gs}^3}\right)}$$

(9)

$$g_{mn} = \frac{1}{n!} \cdot \frac{\partial^n I_D}{\partial V_{gs}^n}.$$

(10)

$R_{\rm S}$  is the system impedance, which is assumed to be 50  $\Omega$  for matched systems. Equation (10) is the general definition of the normalized derivatives of the transconductance. Fig. 6 illustrates the calculated IIP3 for currents of Fig. 5 using (9). Dotted and dashed lines in Fig. 6 respectively show the IIP3 values for 1-D quasi-ballistic devices in the QCL when SRS and OPS prevail in the channel. The thicker solid line shows the IIP3 values for an ideal 1-D ballistic device in the QCL.

While, as discussed above, at a channel potential of 200 meV both devices exhibit identical mfp and current values, the device with OPS has a higher IIP3 value and is more linear. It is apparent from Fig. 4 that OPS has a smaller rate of change of the mean-free-path versus energy than SRS, which is the main reason for the higher linearity value. In order to provide more confidence on the correctness of this conclusion, the same analysis is applied to a device with an unspecified

scattering mechanism with a very small rate of change of (see Fig. 4) compared to SRS and OPS. As evident from Fig. 6, this device shows an even larger IIP3 value than the device under conditions where phonon scattering is dominant in support of our claim from above. While the IIP3 values for the small-channel potentials are limited by Fermi function broadening, the behavior for channel potentials between 100 meV and 200 meV illustrates the effect of  $\lambda(E)$  associated with the various scattering mechanisms. IIP3 values in this paper are higher than the values in our previous work ( $\sim -15$  dBm) in which various scattering mechanisms impact the linearity all at once [15], [16].

These findings show that in devices that operate in the 1-D quasi-ballistic transport regime in the QCL, linearity is directly related to the nature of the dominant-scattering mechanism in the channel. In fact, we conclude that it is not a small mean-free-path but rather a strong energy dependence of the dominant scattering mechanism that impacts the IIP3 value of a device and thus reduces its linearity. Note that while the input capacitance of the device will be in general a function of the channel potential in the QCL, our focus on transconductance linearity of the device is believed to ensure an impact on circuit linearity regardless of circuit topology.

#### V. Conclusion

This paper provided a set of guidelines for material parameters and channel dimensions to fulfill the requirements for operation of nanowire transistors in the QCL when only one 1-D sub-band is involved in carrier transport over a certain energy range  $\Delta E$ . This paper also focused on the effect of carrier backscattering on RF linearity in quasi-ballistic channels by considering various scattering mechanisms. In particular, this paper showed that current linearity was directly related to the nature of the dominant scattering mechanism in the channel. In general, scattering mechanisms that exhibit a smaller rate of change of mean-free-path as a function of energy provide higher current linearity.

### ACKNOWLEDGMENT

The authors would like to thank A. Paul for helpful discussions and S. Mehrotra for providing the band-structure data for InAs nanowires.

#### REFERENCES

- [1] Y. Ding and R. Harjani, *High-Linearity CMOS RF Front-End Circuits*. New York, NY, USA: Springer-Verlag, 2005.

- [2] Y. Ding and R. Harjani, "A CMOS high efficiency +22 dBm linear power amplifier," in *Proc. IEEE Custom Integr. Circuit Conf.*, Oct. 2004, pp. 557–560.

- [3] Y. Ding and R. Harjani, "A +18 dBm IIP3 LNA in 0.35 μm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2001, pp. 162–163.

- [4] H. Zhang, E. Sánchez-sinencio, and L. Fellow, "Linearization techniques for CMOS low noise amplifiers: A tutorial," *IEEE Trans. Syst. Circuits*, vol. 58, no. 1, pp. 22–36, Jan. 2011.

- [5] D. K. Shaeffer, A. Shahani, S. Mohan, H. Samavati, H. Rategh, M. del Mar Hershenson, M. Xu, C. Yue, D. Eddleman, and T. Lee, "A 115-mW, 0.5-μm CMOS GPS receiver with wide dynamic-range active filters," *IEEE J. Solid State Circuits*, vol. 33, no. 12, pp. 2219–2231, Dec. 1998.

- [6] I. Kwon and K. Lee, "An accurate behavioral model for RF MOSFET linearity analysis," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 12, pp. 897–899, Dec. 2007.

- [7] A. O. Adan, T. Yoshimasu, S. Shitara, N. Tanba, and M. Fukurni, "Linearity and low-noise performance of SOI MOSFETs for RF applications," *IEEE Trans. Electron Devices*, vol. 49, no. 5, pp. 881–888, May 2002.

- [8] W. Ma, S. Kaya, and A. Asenov, "Study of RF linearity in sub-50 nm MOSFETs using simulations," J. Solid-State Electron., vol. 2, nos. 2–4, pp. 347–352, Jun. 2004.

- [9] W. Ma and S. Kaya, "Impact of device physics on DG and SOI MOSFET linearity," *J. Comput. Electron.*, vol. 48, nos. 10–11, pp. 1741–1746, Dec. 2003.

- [10] R. Aggarwal, A. Agrawal, M. Gupta, and R. S. Gupta, "Improved linearity performance of AlGaN/GaN MISHFET over conventional HFETs: An optimization study for wireless infrastructure applications," *SuperLatt. Microstruct.*, vol. 50, no. 1, pp. 1–13, Jul. 2011.

- [11] S. Kaya and W. Ma, "Optimization of RF linearity in DG-MOSFETS," *IEEE Electron Device Lett.*, vol. 25, no. 5, pp. 308–310, May 2004.

- [12] L. Yang, A. Asenov, M. Borici, J. R. Watling, J. R. Barker, S. Roy, K. Elgaid, I. Thayne, and T. Hackbarth, "Optimizations of sub-100 nm Si/SiGe MODFETs for high linearity RF applications," in *Proc. IEEE Conf. Electron Devices Solid-State Circuits*, Dec. 2003, pp. 331–334.

- [13] R. Kim and M. S. Lundstrom, "Characteristic features of 1-D ballistic transport in nanowire MOSFETs," *IEEE Trans. Nanotechnol.*, vol. 7, no. 6, pp. 787–794, Nov. 2008.

- [14] J. E. Baumgardner, A. A. Pesetski, J. M. Murduck, J. X. Przybysz, J. D. Adam, and H. Zhang, "Inherent linearity in carbon nanotube field-effect transistors," *Appl. Phys. Lett.*, vol. 91, no. 5, pp. 052107-1–052107-3, 2007.

- [15] A. Razavieh, N. Singh, A. Paul, G. Klimeck, D. Janes, and J. Appenzeller, "A new method to achieve RF linearity in SOI nanowire MOS-FETs," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2011, pp. 1–4.

- [16] A. Razavieh, S. Mehrotra, N. Singh, G. Klimeck, D. Janes, and J. Appenzeller, "Utilizing the unique properties of nanowire MOSFETs for RF applications," *Nano Lett.*, vol. 13, no. 4, pp. 1549–1554, Apr. 2013.

- [17] J. Appenzeller, J. Knoch, and M. T. Bjork, "Toward nanowire electronics," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp. 2827–2845, Nov. 2008.

- [18] R. Granzner, S. Thiele, C. Schippel, and F. Schwierz, "Quantum effects on the gate capacitance of trigate SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 57, no. 12, pp. 3231–3238, Dec. 2010.

- [19] S. Ilani, L. A. K. Donev, M. Kindermann, and P. L. McEuen, "Measurement of the quantum capacitance of interacting electrons in carbon nanotubes," *Nature Phys.*, vol. 2, no. 10, pp. 687–691, Sep. 2006.

- [20] S. M. Sze and K. Ng, Physics of Semiconductor Devices. New York, NY, USA: Wiley, 2007.

- [21] P. Bhattachary, Properties of Lattice-Matched and Strained Indium Gallium Arsenide. Chicago, IL, USA: INSPEC, 1993.

- [22] G. D. Sanders, C. J. Stanton, and Y. C. Chang, "Theory of transport in silicon quantum wires," *Phys. Rev. Lett. B*, vol. 48, no. 15, pp. 11067–11076, 1993.

- [23] M. A. Khayer and R. K. Lake, "Performance of n-type InSb and InAs nanowire field-effect transistors," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp. 2939–2945, Nov. 2008.

- [24] M. A. Khayer and R. K. Lake, "The quantum and classical capacitance limits of InSb and InAs nanowire FETs," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2215–2223, Oct. 2009.

- [25] K. Jansson, E. Lind, and L.-E. Wernersson, "Performance evaluation of III–V nanowire transistors," *IEEE Trans. Electron Devices*, vol. 59, no. 9, pp. 2375–2382, Sep. 2012.

- [26] T. Sadi, J. Thobel, and F. Dessenne, "Self-consistent electrothermal Monte Carlo simulation of single InAs nanowire channel MISFETs," J. Appl. Phys., vol. 108, no. 8, pp. 084506-1–084506-7, 2010

- [27] T. Sadi and R. Kelsall, "Monte Carlo study of the electrothermal phenomenon in SOI and SGOI MOSFETs," J. Appl. Phys., vol. 107, no. 6, pp. 064506-1–064506-9, 2010.

- [28] M. Lundstrom, Fundamentals of Carrier Transport. Cambridge, U.K.: Cambridge Univ. Press, 2000.

- [29] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I—Effects of substrate impurity concentration," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2357–2362, Dec. 1994.

- [30] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part II—Effects of surface orientation," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2363–2368, Dec. 1994.

- [31] R. Landauer, "Spatial variation of currents and fields due to localized scatterers in metallic conduction," *IBM J. Res. Develop.*, vol. 32, no. 3, pp. 306–316, May 1988.

- [32] D. Nikonov, G. Bourianoff, and S. Hasan, (2009). Notes on Scattering and Mobility in 1D, 2D, and 3D [Online]. Available: http://nanohub.org/resources/7738/download/ Mobility\_in 1D 2D\_and 3D 4b.pdf

- [33] G. D. Mahan and J. O. Sofo, "The best thermoelectric," Proc. Nat. Acad. Sci. United States Amer., vol. 93, no. 15, pp. 7436–7439, Jul. 1996.

- [34] N. Neophytou and H. Kosina, "Numerical study of the thermoelectric power factor in ultra-thin Si nanowires," J. Comput. Electron., vol. 11, no. 1, pp. 29–44, Jan. 2012.

- [35] B. Razavi, RF Microelectronics. Englewood Cliffs, NJ, USA: Prentice-Hall, 1998.

Authors' photographs and biographies not available at the time of publication.