## Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

April 2007

## Photo-assisted capacitance-voltage characterization of high-quality atomic-layer-deposited Al2O3/GaN metal-oxide-semiconductor structures

Y Q. Wu

Purdue University

T Shen

Purdue University

P.D. Ye

Birck Nanotechnology Center and School of Electrical and Computer Engineering, Purdue University, yep@purdue.edu

GD. Wilk

ASM America

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub

Wu, Y Q.; Shen, T; Ye, P. D.; and Wilk, G D., "Photo-assisted capacitance-voltage characterization of high-quality atomic-layer-deposited Al2O3/GaN metal-oxide-semiconductor structures" (2007). *Birck and NCN Publications*. Paper 242. http://docs.lib.purdue.edu/nanopub/242

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## Photo-assisted capacitance-voltage characterization of high-quality atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub>/GaN metal-oxide-semiconductor structures

Y. Q. Wu, T. Shen, and P. D. Yea

School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907 and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907

G. D. Wilk

ASM America, 3440 East University Drive, Phoenix, Arizona 85034

(Received 21 December 2006; accepted 1 March 2007; published online 2 April 2007)

The authors report on an  $Al_2O_3$  gate oxide deposited on n-type GaN by atomic layer deposition technique. The high-frequency C-V characteristic shows deep-depletion behavior at room temperature due to the wide band gap semiconductor nature of GaN. Systematic photoassisted C-V measurements demonstrate the importance of postdeposition-annealing process which could improve the average interface trap density  $D_{it}$  of  $(1-2)\times 10^{12}/\text{cm}^2\,\text{eV}$  on the as-grown films to  $7 \times 10^{10}$ /cm<sup>2</sup> eV on the same films after 800 °C rapid thermal annealing in a N<sub>2</sub> ambient. The high-frequency C-V technique or Terman technique is also applied to estimate the mid-gap  $D_{\rm it}$  and compare to the results from photoassisted C-V technique. © 2007 American Institute of Physics. [DOI: 10.1063/1.2719228]

GaN is a promising semiconductor electronic material for applications in high-temperature, high-speed, and highpower electronics due to its fundamental physical properties such as wide band gap and high saturation velocity. The progress made in GaN electronic device field in the past decade is astonishing. One of the major factors that limit the performance and reliability of GaN high-electron-mobility transistors (HEMTs) to be finally commercialized for rf highpower applications is their relatively high gate leakage and its stability of Schottky contacts at high temperatures. The gate leakage reduces the breakdown voltage and the poweradded efficiency while increasing the noise figure. To help solve the problem, the use of atomic-layer-deposited (ALD) gate dielectrics adopted from the state-of-the-art Si complementary metal-oxide-semiconductor (CMOS) technology could be one of the attractive solutions.

In the research front of dielectrics on GaN, significant progress has also been made on GaN metal-insulatorsemiconductor high-electron-mobility transistors (MIS-HEMTs) and GaN metal-oxide-semiconductor high-electronmobility transistors (MOS-HEMTs) using  $SiO_2$ ,  $^{2-6}$   $Si_3N_4$ ,  $^{7-9}$   $Al_2O_3$ ,  $^{10,11}$  and other oxides.  $^{12}$  Recently, there is a growing interest in exploring GaN metal-oxide-semiconductor fieldeffect transistors (MOSFETs) for digital applications because GaN devices could provide low off drain currents, excellent transport properties, high-quality epilayers on Si, and material compatibility for Si process temperatures. Furthermore, GaN based electronic devices could find wide applications by integrating with GaN optoelectronic devices. The major motivation on GaN MOSFET research is to realize highperformance enhancement mode<sup>13</sup> or even inversion-type devices<sup>14</sup> with scalable gate dielectrics. ALD is a surface controlled layer-by-layer process for the deposition of thin films with atomic layer accuracy. Each atomic layer formed in the sequential process is a result of saturated surface controlled chemical reactions. The thickness control of the ALD

films, which is very important for MOSFET scalability, is much superior to the control ability of SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub> using plasma-enhanced chemical-vapor deposition. The ALD Al<sub>2</sub>O<sub>3</sub> process is *ex situ*, robust, and highly manufacturable. Al<sub>2</sub>O<sub>3</sub> offers additional advantages of a large band gap (9 eV), high dielectric constant ( $k \sim 8.6-10$ ), high breakdown field (10-30 MV/cm), thermal stability, and chemical stability against GaN. Furthermore, ALD is the most promising approach to high-k dielectrics (i.e., HfSiON) and given Si industry's familiarity with ALD for front-end processes. the transition to ALD GaN MOSFETs integrated on Si CMOS platform must be easier. We reported earlier highperformance GaN MOS-HEMTs and depletion-mode GaN MOSFETs with ALD  ${\rm Al_2O_3.}^{11,15}$  In this Letter, we report on the systematic photoassisted C-V studies of ALD Al<sub>2</sub>O<sub>3</sub>/GaN MOS structures. The excellent MOS interface property is a must to realize high-performance inversion type of GaN enhancement-mode MOSFETs.

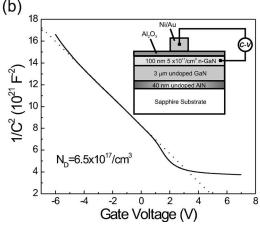

The cross section of an ALD Al<sub>2</sub>O<sub>3</sub>/GaN MOS capacitor is shown in the inset of Fig. 1(b). A 40 nm undoped AlN buffer layer, a 3  $\mu m$  undoped GaN layer, and a 100 nm, 5  $\times 10^{17}$ /cm<sup>3</sup> Si-doped GaN layer were sequentially grown by metal-organic chemical vapor deposition on a 2 in. sapphire substrate. After the standard RCA cleaning, the wafers were transferred via room ambient to an ASM Pulsar2000TM ALD module. A 40-nm-thick Al<sub>2</sub>O<sub>3</sub> layer was deposited at a substrate temperature of 300 °C using alternately pulsed chemical precursors of Al(CH<sub>3</sub>)<sub>3</sub> (the Al precursor) and H<sub>2</sub>O (the oxygen precursor) in a carrier N2 gas flow. A 200-nm-thick Ni/Au layer was electron-beam deposited and lithographically defined to form circular MOS capacitors with various diameters. Since the n-type GaN layer is epitaxially grown on an insulating sapphire substrate, electrical contact to the GaN layer in this work was made via a serial capacitor with an area of approximately 1000 times larger than that of the device under study. An HP4284 LCR meter was used for the capacitance measurement. The samples were measured sequentially after they underwent a postmetal-deposition annealing (PMA) of 600-800 °C. The similar results are ob-

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed; electronic mail: yep@purdue.edu

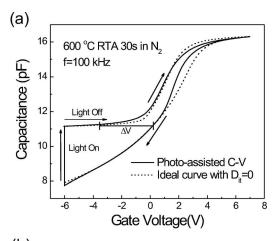

FIG. 1. (a) Photoassisted C-V curves on a n-type GaN MOS capacitor at room temperature. The sample is swept from accumulation to deep depletion in the dark, held at -6 V and illuminated to form an inversion layer, then swept back to accumulation in the dark. The dashed lines are theoretical calculated curves with  $D_{\rm it}$ =0 and the dielectric constant of 7.2. The area of the measured capacitor is  $\sim 1.0 \times 10^{-4} / {\rm cm}^2$ . (b)  $1/{\rm C}^2$  characteristics as a function of gate voltage.  $N_d$  obtained from the slope is  $6.5 \times 10^{17} / {\rm cm}^3$ . The dotted line is a guide to the eyes. Inset: schematic view of a GaN capacitor MOCVD grown on sapphire with ALD grown  ${\rm Al}_2{\rm O}_3$  as gate dielectric.

tained for postdielectric-deposition annealing (PDA).

The high-frequency C-V technique, or Terman technique, is the simplest and most straightforward method for characterizing the interface trap density  $D_{\rm it}$  at the SiO<sub>2</sub>/Si interface. Unfortunately, this technique does not work well for wide band gap semiconductors such as GaN and can lead to gross underestimation of the interface trap density at room temperature. A quick method for estimating the total number of interface states across the band gap is the room temperature photo-CV technique, developed by Tan *et al.* for SiC (Ref. 16) and other groups for GaN. The solid curves in Fig. 1(a) show typical photoassisted C-V curves measured at room temperature. The gate voltage is swept from accumulation (positive voltage) to depletion (negative voltage) in the dark. A further increase in the negative bias would result in a continual depletion of the GaN, instead of the buildup of an inversion layer, because the minority-carrier generation rate is exceedingly slow for GaN wide band gap semiconductor. Electrons initially captured in the deep-level states cannot emit to the conduction band at room temperature because the emission time constant increases exponentially with energy separation according to the Shockley-Read-Hall statistics. However, if the bias is held at -6 V and the sample is illuminated to populate the inversion layer, a different C-V

curve emerges. As photogeneration populates the inversion layer, the capacitance rises toward the equilibrium value. After the inversion layer is fully formed, the light is turned off and the sample is swept back toward accumulation. The voltage shift  $\Delta V$  is caused by electrons trapped in interface states and can be used to estimate the average  $D_{it}$  across the band gap. This "hysteresis" reflects differences in charging conditions of deep-lying interface states with and without illumination. From the voltage shift  $\Delta V$ , the average  $D_{it}$  can be estimated using the simple equation of  $D_{it} = C_{ox} \Delta V / q E_g$ , 16 where  $D_{it}$  is the average value of interface trap density,  $C_{ox}$  is the oxide capacitance, q is the electron charge, and  $E_g$  is the band gap of GaN. The average  $D_{it}$  of ALD Al<sub>2</sub>O<sub>3</sub>/GaN is about  $(5-6) \times 10^{11}$ /cm<sup>2</sup> eV on 600 °C annealed films, as shown in Fig. 1(a). For an ideal deep-depletion capacitor, coming down in gate voltage from high accumulation,  $d(1/C^2)/dV_g$  curve drops from close to zero to a negative point, and then rises steeply to a negative plateau around "threshold" voltage. The negative value of the plateau is directly related with the majority-carrier concentration  $N_e$  in GaN since  $d(1/C^2)/dV_g = -2/q\varepsilon_s N_e$ .<sup>21</sup> The  $\Delta V$  in this letter is determined by the subtraction of two threshold voltage values from the  $d(1/C^2)/dV_g$  vs  $V_g$  curves for deep depletion and after illumination. A "unique" parallel rising feature is observed on each two correlated curves in all 16 experimental data sets. The insight of device physics of this parallel feature is under further investigation.

Theoretically calculated ideal high-frequency C-V curves is also shown in Fig. 1(a) as dashed lines along with the experimental curves before and after light illumination. The net donor density  $N_d$  of  $6.9 \times 10^{17}$ /cm<sup>3</sup>, which is near the experimental fitting in Fig. 1(b), and zero minority carrier is used for deep-depletion C-V calculation and  $N_d$  of 6.9  $\times 10^{17}$ /cm<sup>3</sup> and hole carrier density p of  $3.0 \times 10^{8}$ /cm<sup>3</sup> is used for C-V curve after illumination. All device parameters, such as the electron affinity of GaAs and metal gate work function, are appropriately chosen by assuming the lowest  $D_{\rm it}$  in GaN located near the mid-band-gap such as Si. These two curves are analyzed using Terman technique. The estimated mid-gap  $D_{\rm it}$  is around  $5 \times 10^{10}/{\rm cm}^2\,{\rm eV}$ , which is about one order of magnitude better than the value obtained from photoassisted C-V method. This leads us to conclude that photoassisted C-V measurement is a more reliable technique to study the interface properties of GaN MOS capacitors and to use the Terman technique at room temperature for wide band gap semiconductors in general could grossly underestimate the actual  $D_{it}$ .

We plot the deep depletion curve of ALD Al<sub>2</sub>O<sub>3</sub>/GaN after 600 °C RTA annealing in a N<sub>2</sub> ambient as  $1/C^2$  versus gate bias V in Fig. 1(b). By fitting the  $1/C^2$  vs V curve, the net donor density  $N_d$  is extracted to be  $6.5 \times 10^{17}/\text{cm}^3$ , which is reasonably close to the electron density of 5.0  $\times 10^{17}/\text{cm}^3$  in the conducting channel determined by Hall measurements. The good linear fitting in the depletion region suggests the decent quality of interface and negligible fixed charge in the insulator.

Systematic photoassisted C-V studies on ALD electrons initially captured in the deep-level states cannot mit to the conduction band at room temperature because the mission time constant increases exponentially with energy eparation according to the Shockley-Read-Hall statistics. However, if the bias is held at -6 V and the sample is illuninated to populate the inversion layer, a different C-V Downloaded 08 Jan 2009 to 128.46.220.88. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

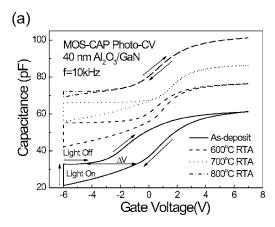

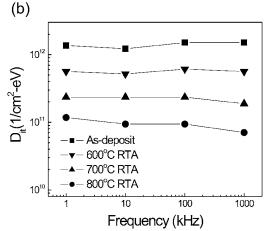

FIG. 2. (a) Photoassisted C-V curves as a function of PMA annealing processes. The area of the measured capacitors is  $\sim 4.0 \times 10^{-4}/\text{cm}^2$ . The curves are shifted vertically for clarity. The absolute values of accumulation capacitance have minor changes due to the change of dielectric constant after different PMA anneals. (b) The calculated average  $D_{it}$  vs measured ac frequency as a function of PMA annealing temperatures.

tures. The narrow or negligible hysteresis on 700 or 800 °C annealed devices suggests that the PDA or PMA is a necessary process step to achieve a low interface trap density on MOS structures. Note that no interface-state ledges on the return sweeps are observed on all photoassisted C-V curves. Figure 2(b) summarizes the obtained average  $D_{it}$  from photoassisted C-V measurements versus different measured ac frequencies as a function of the PMA processes. After 800 °C annealing, the  $D_{\rm it}$  drops from the low  $10^{12}/{\rm cm}^2\,{\rm eV}$ obtained from as-grown devices to  $7 \times 10^{10}$ /cm<sup>2</sup> eV. The average  $D_{\rm it}$  of  $7 \times 10^{10}/{\rm cm^2~eV}$  is one of the best value reported on GaN MOS structures in literatures. ALD Al<sub>2</sub>O<sub>3</sub> starts to be partially crystallized above 825 °C annealing and becomes unfavorable as a gate dielectric. The ideal annealing temperature for ALD Al<sub>2</sub>O<sub>3</sub>/GaN should be between 700 and 800 °C. Some interdiffusion or chemical reaction could occur at the interface after 800 °C PMA, as shown as the less-deep-depletion C-V curve in Fig. 2(a). Note that the leakage current of all above measured Al<sub>2</sub>O<sub>3</sub> films under the typical operating biases is extremely low (below  $10^{-8} \text{ A/cm}^2$ ).

In summary. electrical characterization of ALD  $Al_2O_3/GaN$  interfaces are carried out by the systematic photoassisted C-V measurements. The average  $D_{it}$  of  $7 \times 10^{10}/\text{cm}^2\,\text{eV}$  is achieved after the devices underwent  $800\,^{\circ}\text{C}$  RTA annealing. The high-quality  $Al_2O_3/GaN$  interface provides the opportunity to realize high-performance inversion-type GaN MOSFETs integrated with high-k dielectrics in the Si CMOS platform.

The authors would like to thank J. A. Cooper, M. Lundstrom, B. Yang, Y. Xuan, and W. Z. Chen for the valuable discussions. This work was supported in part by NSF (Grant No. ECS-0621949) and the MARCO MSD Focus Center.

<sup>1</sup>Y.-F. Wu, M. Moore, A. Saxler, T. Wisleder, and P. Parikh, Proceedings of the 64th IEEE Device Research Conference, 2006 (unpublished), pp. 151–152.

<sup>2</sup>M. Asif Khan, X. Hu, G. Sumin, A. Lunev, J. Yang, R. Gaska, and M. S. Shur, IEEE Electron Device Lett. **21**, 63 (2000).

<sup>3</sup>M. Asif Khan, X. Hu, A. Tarakji, G. Simin, J. Yang, R. Gaska, and M. S. Shur, Appl. Phys. Lett. 77, 1339 (2000).

<sup>4</sup>G. Simon, X. Hu, N. Ilinskaya, A. Kumar, A. Koudymov, J. Zhang, M. A. Khan, R. Gaska, and M. S. Shur, Electron. Lett. 36, 2043 (2000).

<sup>5</sup>A. Koudymov, X. Hu, K. Simin, G. Simin, M. Ali, J. Yang, and M. Asif Khan, IEEE Electron Device Lett. **23**, 449 (2002).

<sup>6</sup>G. Simin, A. Koudymov, H. Fatima, J. Zhang, J. Yang, M. Asif Khan, X. Hu, A. Tarakji, R. Gaska, and M. S. Shur, IEEE Electron Device Lett. **23**, 458 (2002).

<sup>7</sup>G. Simon, X. Hu, N. Ilinskaya, J. Zhang, A. Tarakji, A. Kumar, J. Yang, M. Asif Khan, R. Gaska, and M. S. Shur, IEEE Electron Device Lett. 22, 53 (2001).

<sup>8</sup>X. Hu, A. Koudymov, G. Simon, J. Yang, M. Asif Khan, A. Tarakji, M. S. Shur, and R. Gaska, Appl. Phys. Lett. **79**, 2832 (2000).

<sup>9</sup>M. Higashiwaki, T. Mimura, and T. Matsui, IEEE Electron Device Lett. 27, 719 (2006).

<sup>10</sup>T. Hashizume, S. Ootomo, and H. Hasegawa, Appl. Phys. Lett. 83, 2952 (2003).

<sup>11</sup>P. D. Ye, B. Yang, K. Ng, J. Bude, G. D. Wilk, S. Halder, and J. C. M. Hwang, Appl. Phys. Lett. **86**, 063501 (2005).

<sup>12</sup>R. Mehandru, B. Luo, J. Kim, F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy, S. J. Pearton, D. Gotthold, R. Birkhahn, B. Peres, R. Fitch, J. Gillespie, T. Jenkins, J. Sewell, D. Via and A. Crespo, Appl. Phys. Lett. 82, 2530 (2003).

<sup>13</sup>R. Wang, Y. Cai, C.-W. Tang, K. M. Lau, and K. J. Chen, IEEE Electron Device Lett. **27**, 793 (2006).

<sup>14</sup>W. Huang, T. Khan, and T. P. Chow, IEEE Electron Device Lett. 27, 796 (2006).

<sup>15</sup>Y. Q. Wu, P. D. Ye, G. D. Wilk, and B. Yang, Mater. Sci. Eng., B **135**, 282 (2006).

<sup>16</sup>J. Tan, M. K. Das, J. A. Cooper, and M. R. Melloch, Appl. Phys. Lett. **70**, 2280 (1997).

<sup>17</sup>T. Hashizume, E. Alekseev, D. Pavlidis, K. S. Boutros, and J. Redwing, J. Appl. Phys. 88, 1983 (2000).

<sup>18</sup> H. C. Casey, G. G. Fountain, R. G. Alley, B. P. Keller, and S. P. DenBaars, Appl. Phys. Lett. **68**, 1850 (1996).

<sup>19</sup>B. Gaffey, L. J. Guido, X. W. Wang, and T. P. Ma, IEEE Electron Device Lett. 48, 458 (2001).

<sup>20</sup>C. Bae and G. Lucovsky, J. Vac. Sci. Technol. A **22**, 2402 (2004).

<sup>21</sup>S. M. Sze and Kwok K. Ng, *Physics of Semiconductor Devices*, 3rd ed. (Wiley-Interscience, New Jersey, 2007), p. 85.

W. Huang, T. Khan, and T. P. Chow, J. Electron. Mater. 35, 726 (2006).

C. Bae, C. Krug, G. Lucovsky, A. Chakraborty, and U. Mishra, J. Appl. Phys. 96, 2674 (2004).