# Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

11-29-2006

## Self-heating simulation of GaN-based metal-oxidesemiconductor high-electron-mobility transistors including hot electron and quantum effects

W.D.Xu

National Laboratory for Infrared Physics, Shanghai Institute of Technical Physics, Chinese Academy of Sciences

X. S. Chen

National Laboratory for Infrared Physics, Shanghai Institute of Technical Physics, Chinese Academy of Sciences

Z. J. Quan

National Laboratory for Infrared Physics, Shanghai Institute of Technical Physics, Chinese Academy of Sciences

C. S. Xia

National Laboratory for Infrared Physics, Shanghai Institute of Technical Physics, Chinese Academy of Sciences

W. Lu

National Laboratory for Infrared Physics, Shanghai Institute of Technical Physics, Chinese Academy of Sciences

See next page for additional authors

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub

Xu, W. D.; Chen, X. S.; Quan, Z. J.; Xia, C. S.; Lu, W.; and Ye, P. D., "Self-heating simulation of GaN-based metal-oxide-semiconductor high-electron-mobility transistors including hot electron and quantum effects" (2006). *Birck and NCN Publications*. Paper 19. http://docs.lib.purdue.edu/nanopub/19

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

| Authors<br>W. D. Xu, X. S. Chen, Z. J. Quan, C. S. Xia, W. Lu, and P. D. Ye |  |  |  |

|-----------------------------------------------------------------------------|--|--|--|

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

|                                                                             |  |  |  |

# Self-heating simulation of GaN-based metal-oxide-semiconductor high-electron-mobility transistors including hot electron and quantum effects

W. D. Hu, X. S. Chen, a) Z. J. Quan, C. S. Xia, and W. Lu<sup>b)</sup> *National Laboratory for Infrared Physics, Shanghai Institute of Technical Physics, Chinese Academy of Sciences, Shanghai 200083, China*

P. D. Ye

School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907 and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907

(Received 27 December 2005; accepted 25 July 2006; published online 3 October 2006)

Undoped GaN-based metal-oxide-semiconductor high-electron-mobility transistors (MOS-HEMTs) with atomic-layer-deposited  $Al_2O_3$  gate dielectrics are fabricated with gate lengths from 1 up to 40  $\mu$ m. Using a two-dimensional numerical simulator, we report the results of self-heating simulations of the GaN-based MOS-HEMTs, including hot electron and quantum effects. The simulated electrical characteristics are in good agreement with reported experimental data. The effect of the gate and source/drain extension lengths on both the output performance and self-heating is discussed in detail, allowing for device optimization. The dissipated Joule electric power causes the self-heating effects, which lead to negative differential output conductance. Our results demonstrate that the hot electrons make a negligible contribution to the negative differential output conductance in our long channel MOS-HEMTs. In order to investigate their joint interactions to the MOS-HEMT's operation, the different static interface trap and charge densities created at the AlGaN/Al $_2O_3$  interface are considered in the output characteristics. Results show that the presence of the interface charges and traps are directly responsible for the observed current collapse and device switching in the GaN-based MOS-HEMTs. The self-heating is also strongly affected due to the fluctuation of the interface states. © 2006 American Institute of Physics.

#### [DOI: 10.1063/1.2354327]

#### I. INTRODUCTION

Recent advances in GaN-based high-electron-mobility transistors (HEMTs) have opened the way for their practical applications in high power and high frequency electronic devices. However, the typically large gate leakage current reduces the breakdown voltage, power-added efficiency, and device reliability, in addition to increasing the noise figure. The leakage current is thus an important roadblock to achieve the practical applications of these devices. To solve the problem, significant progress has been made on metalinsulator-semiconductor high-electron-mobility transistors (MIS-HEMTs) and metal-oxide-semiconductor electron-mobility transistors (MOS-HEMTs) using SiO<sub>2</sub>,  $^{1-5}$  Si<sub>3</sub>N<sub>4</sub>,  $^{6,7}$  Al<sub>2</sub>O<sub>3</sub>,  $^{8,9}$  and other oxides.  $^{10}$  Recently, Ye *et al.*  $^{11}$ have reported a GaN-based MOS-HEMT with atomic-layerdeposited (ALD) Al<sub>2</sub>O<sub>3</sub> as the gate dielectric, showing low leakage current, high breakdown voltage, strong accumulation, and high effective two-dimensional (2D) electron mobility under both low and high transverse fields. ALD Al<sub>2</sub>O<sub>3</sub> has been widely studied as a gate dielectric and has become one of the leading candidates to replace SiO2 in futuregeneration Si complementary metal-oxide semiconductor (CMOS) digital integrated circuits (ICs). 12,13 However,

significant self-heating effects have been found in the MOS-HEMTs when operating under high power.

The elimination of the self-heating effects requires an understanding of the physical phenomena responsible for them. The physics-based numerical simulation provides an efficient and economical way for complementing experimental investigations. However, there have only been a few reports on the self-heating simulation of the GaN-based HEMTs. Wu et al. have reported a thermal simulation using a 2D steady-state heat conduction model. <sup>14,15</sup> Eastman *et al.* have carried out nonlinear three-dimensional heat spreading simulations as functions of the dissipated power and the device geometry. 16 Albrecht et al. have presented a gradualchannel-approximation-based Monte Carlo simulation of the GaN-based HEMTs. 17 Ahmad et al. have carried out a 2D finite element self-heating analysis of the GaN-based HEMTs. 18 Braga et al. have reported 2D steady-state simulations of the GaN-based HEMTs by considering the hot electron and the quantum effects. <sup>19</sup> The GaN-based HEMT is a complicated device with multiple interfaces, which play an important role in the self-heating effects and the device operations. However, the reported simulations have not taken into account the interface charges or traps at all of the interfaces. All reported simulations, except for Braga et al., have neglected the quantum effects of the nanoscale GaN-based HEMTs. Furthermore, no publications have been dedicated to the self-heating simulation of the GaN-based MOS-

<sup>&</sup>lt;sup>a)</sup>Electronic mail: xschen@mail.sitp.ac.cn <sup>b)</sup>Electronic mail: luwei@mail.sitp.ac.cn

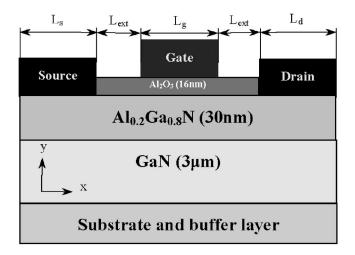

FIG. 1. Schematic structure of GaN-based MOS-HEMT with  $\mathrm{Al_2O_3}$  gate dielectric.

HEMTs. It is well recognized from the experimental data that it is necessary to optimize the geometry of the current devices, especially for the source/drain extension and the Al<sub>2</sub>O<sub>3</sub>/AlGaN interface.

In order to understand and control the self-heating effects and the trap-related drain current, we perform 2D simulations of the GaN-based MOS-HEMTs taking into account the self-heating effects. The structural and interfacial optimizations of the MOS-HEMTs are also discussed. The simulation tool, whose validity in the GaN-based HEMTs has been established in Refs. 19 and 20, is the multidimensional device simulator DESSIS from Integrated Systems Engineering. <sup>21</sup>

#### II. DEVICE DESCRIPTION AND SIMULATION MODEL

Figure 1 shows the cross sections of the ALD Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN-based MOS-HEMT. A 40 nm undoped AlN buffer layer, a 3  $\mu$ m undoped GaN layer, and a 30 nm undoped Al<sub>0.2</sub>Ga<sub>0.8</sub>N layer are sequentially grown by metalorganic chemical vapor deposition on a 2 in. sapphire substrate. After these layers are grown, the wafer is transferred via room ambient to an ASM Pulsar2000TM ALD module. A 16-nm-thick Al<sub>2</sub>O<sub>3</sub> layer is deposited at 300 °C, followed by annealing at 600 °C per 60 s in oxygen ambient. Device isolation is achieved by nitrogen implantation. Using a wet etch in diluted HF, the oxide on the source and drain regions is removed while the gate region is protected by photoresist. Ohmic contacts are formed by electron-beam deposition of Ti/Al/Ni/Au and a lift-off process, followed by an 850 °C anneal in nitrogen ambient, which also activates the previously implanted nitrogen. Finally, Ni/Au metals are e beam evaporated and lifted off to form the gate electrodes. All four levels of lithography (alignment, isolation, Ohmic, and gate) are done by using a contact aligner. The gate width  $(W_{o})$  is 100  $\mu$ m, the gate length ( $L_g$ ) varies from 1 to 40  $\mu$ m (most of the simulations are concentrated on 5  $\mu$ m), the source and drain lengths ( $L_s$  and  $L_d$ ) are 5  $\mu$ m for the simulations, and the source/drain extension  $(L_{\text{ext}})$  is 2  $\mu$ m.

To account for the self-heating, the nonisothermal model available in DESSIS is utilized. The temperature gradient

drift-diffusion transport equations and the temperature distribution equations are calculated self-consistently. Since the hot electrons have a significant effect on the vertical real space charge transfer and subsequent capture in bulk traps, <sup>19,20</sup> they are accounted for by the hydrodynamic transport model available in DESSIS. Mobility of GaN in the device grown on the sapphire substrate is approximately 1000 cm<sup>2</sup>/V s. <sup>22</sup>

The electric fields induced by the high piezoelectric and spontaneous polarization lead to a significant increase in the sheet carrier concentration and a more narrow confinement of the two-dimensional electron gas (2DEG) at the AlGaN/GaN heterointerface without doping in wurtzite group-III nitrides HEMTs. <sup>23–26</sup> In the absence of the external fields, the effect of the polarization leads to sheet interface charge accumulation on the end of the crystals. These interface charges are, of course, equal in magnitude and opposite in sign to maintain overall charge neutrality and will induce free carriers to compensate themselves. Theoretical computations of the interface charges of the GaN-based MOS-HEMT due to the high piezoelectric and spontaneous polarization are given as follows. <sup>27,28</sup>

The strain-induced piezoelectric polarization of  $Al_xGa_{(1-x)}N$  can be expressed by

$$P_{\text{pz\_AlGaN}}(x) = 2 \times \varepsilon_{xx} \times \left(e_{31} - \frac{c_{13}}{c_{33}} \times e_{33}\right),\tag{1}$$

$$\varepsilon_{xx} = \frac{\left[a_{\text{GaN}} - a_{\text{AlGaN}}(x)\right]}{a_{\text{AlGaN}}(x)}.$$

(2)

The charge due to the piezopolarization variation at the AlGaN/GaN interface is given by

$$D_{\text{PDZ}} = 0 - P_{\text{DZ AlGaN}}(x), \tag{3}$$

where a is the crystal lattice constant. A linear interpolation between the lattice constant of GaN and AlN is used on the calculation of  $a_{AlGaN}(x)$ .  $\varepsilon_{xx}$  is the strain of the x-y plane,  $c_{13}$  and  $c_{33}$  are the elastic constants,  $e_{33}$  and  $e_{31}$  are the piezoelectric constants given as follows:

$$e_{33} = [x \times 1.46 \times 10^{-4} + (1 - x) \times 0.73 \times 10^{-4}]/q,$$

(4)

$$e_{31} = [x \times (-0.60 \times 10^{-4}) + (1 - x) \times (-0.49 \times 10^{-4})]/q,$$

(5)

$$c_{13} = x \times 108 + (1 - x) \times 103,$$

(6)

$$c_{33} = x \times 373 + (1 - x) \times 405. \tag{7}$$

The spontaneous polarization of  $Al_{(1-x)}Ga_xN$  is also a function of Al mole fraction x and can be expressed by

$$P_{\rm sp\ AlGaN}(x) = x \times P_{\rm sp\ AlN} + (1 - x) \times P_{\rm sp\ GaN}.$$

(8)

The charge due to the spontaneous polarization at the AlGaN/GaN interface is given by

$$D_{\text{Psp}} = P_{\text{sp\_GaN}} - P_{\text{sp\_AlGaN}}(x). \tag{9}$$

Finally, the interface charge induced by the polarization at the AlGaN/GaN interface is included in our simulation as  $D+D_{Ppz}$ . The interface charge at the AlGaN/Al<sub>2</sub>O<sub>3</sub> interface is  $P_{sp\_AlGaN}(x)+P_{pz\_AlGaN}(x)$  and  $-(P_{sp\_GaN})$  for the GaN/buffer interface. All of the parameters in Eqs. (1)–(9) can be found in Refs. 27 and 28.

Due to a large conduction band offset in AlGaN/GaN, some studies have indicated that the 2DEG induced by the polarization are subject to quantum confinement within 2-5 nm (Refs. 27 and 29) at the AlGaN/GaN interface. For example. Ambacher et al. have shown that the confined carriers are within 2 nm of the AlGaN/GaN interface. 27 Based on the C-V-concentration experiments, Yu et al. have found that the 2DEG arising from the polarization would be located within 2–5 nm of the AlGaN/GaN interface. <sup>29</sup> Furthermore, Braga et al. have shown using a self-consistent calculation that the 2DEG quantum confinement is within 2-5 nm of the AlGaN/GaN interface. 19 Therefore, the quantum effects become noticeable at the AlGaN/GaN interface. Methodologies and models for the GaN MOS-HEMTs must be used for the device simulations to account for these effects. Since the density-gradient (DG) model is robust, fast, and can be applied to highly nonequilibrium situations, <sup>21</sup> the quantized electron gas has been accounted for by the DG transport model.<sup>30</sup> The DG approach is a self-consistent way to account for the quantum effects via the quantum potential correction to the continuity equation.<sup>31</sup>

The trap density and cross sections in III-nitride materials have been shown in some experimental observations and theoretical calculations such as Refs. 32 and 33. Here, we assume just a single acceptor type electron bulk trap level with a trap density of  $1.0 \times 10^{18}$  cm<sup>-3</sup> and a cross section of  $\sigma_{\rm Tn} = 1.0 \times 10^{-15} \, {\rm cm}^{-2}$ , and position it 1 eV above midband-gap. <sup>19,29,32,33</sup> The thermal conductivity ( $\kappa$ ) of GaN is known to depend on dislocation density  $(\rho_D)$ , <sup>34</sup> which varies along the epitaxial growth direction. We divide the GaN layer into two layers in our simulation. The first layer is the 150 nm initial growth region, with  $\kappa = 1.3 \text{ W cm}^{-1} \text{ K}^{-1}$ ; the remainder of the GaN layer has  $\rho_D < 10^{10} \ \rm cm^{-2}$  and  $\kappa = 1.5 \ \rm W \ cm^{-1} \ K^{-1}.^{34}$  Since the thin AlGaN layer plays a minor role in dissipating heat, we employ the properties of GaN. We use  $\kappa = 0.28 \text{ W cm}^{-1} \text{ K}^{-1}$  for the sapphire <sup>34,35</sup> and ignore its temperature dependence since the observed  $\Delta T$  rise is small. Parameters of Al<sub>2</sub>O<sub>3</sub>, being very important to our MOS-HEMT simulations, are extracted from Refs. 9 and 11. The estimated oxide thickness  $(d_{OX})$  is 10 nm, which is significantly less than the design value of 16 nm.

#### **III. QUANTIZATION AND SELF-HEATING EFFECTS**

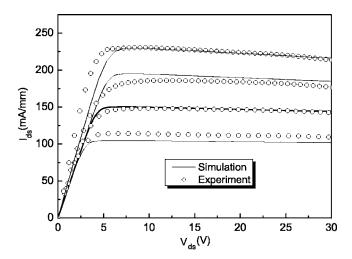

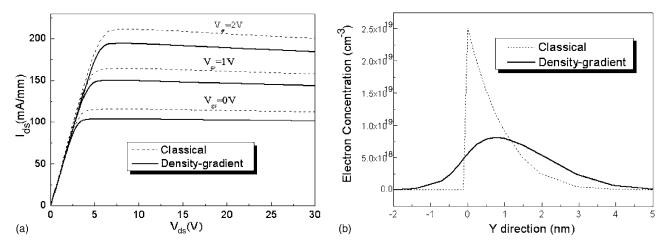

Figure 2 shows the simulated and experimental dc output characteristics ( $I_{\rm ds}$ - $V_{\rm ds}$ ) of the MOS-HEMT for  $V_{\rm gs}$  values varying from 0 to 3 V in 1 V steps. It is found that the simulation results are in good agreement with the experiment data. All of the curves display the distinct negative differential output conductance (NDC) due to the self-heating effects. Figure 3(a) compares the simulated and experimental transfer characteristics ( $I_{\rm ds}$ - $V_{\rm gs}$ ). The simulations are performed with and without the thermodynamics model. Because the  $I_{\rm ds}$ - $V_{\rm gs}$  curves with and without the thermodynamics model are quite similar, the transfer characteristics are not

FIG. 2. Simulated and experimental  $I_{\rm ds}$ - $V_{\rm ds}$  of MOS-HEMT. Experiment (circles) and simulation (solid lines) with thermodynamic and DG approaches for  $V_{\rm gs}$ =0, 1, 2, and 3 V.

greatly affected by the self-heating effects from under 10 V gate voltage, which is in good agreement with the measurements. Figure 3(b) shows the experimental  $I_{\rm ds}$ - $V_{\rm ds}$  under 10 V drain voltage. No NDC is found because no serious self-heating comes out under the low drain voltage.

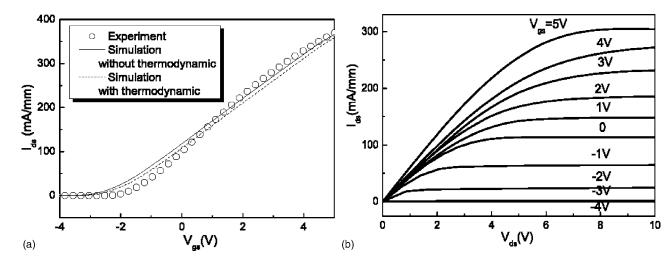

Figure 4(a) shows the current-voltage  $(I_{ds}-V_{ds})$  as predicted by a classical simulation and as predicted with the DG model. The simulation results reveal that the current predicted with the DG model is suppressed by approximately 9.6% due to the carrier confinement that arises when the quantum approach is chosen. We can also note that the data from the quantum method agree more closely to that of the experimental data. Figure 4(b) shows the corresponding distribution of electrons in the channel under the zero bias conditions. It is evident that the classical picture does not account for the quantum confinement of electrons. Both the quantum approaches and the classical simulations yield similar values for the sheet electron density  $n_s \approx 6 \times 10^{12} \text{ cm}^{-2}$ , which is in good agreement with the experimentally measured value. However, the classical approach does not account for the significant penetration of the electron wave function into the AlGaN barrier layer and the GaN bulk layer. The quantum calculations clearly show a significant penetration of the electron wave function from the 2D gas into three-dimensional states in AlGaN and GaN, thereby reducing the electron mobility and the drain current [Fig. 4(a)].

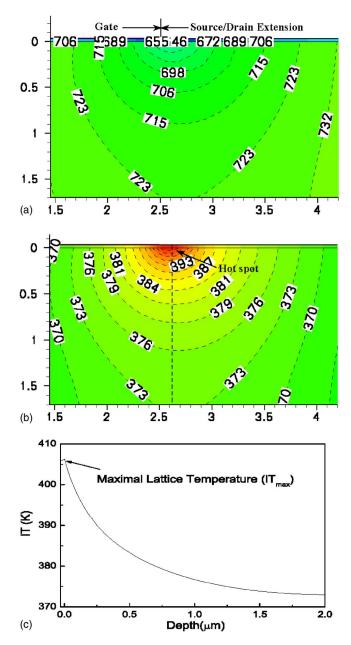

The self-heating is a local increase of crystal temperature due to dissipated Joule electric power. Tigure 5(a) shows the electron mobility contour map for the GaN-based MOS-HEMT at the drain-side gate edge. Figure 5(b) shows the self-heating simulation of the electron temperature contour map with the hot spot clearly visible at the drain-side gate edge. The heat conduction has the expected effect of broadening the hot spot. The vertical dashed line illustrates the cut place of Fig. 5(c). Figure 5(c) shows the simulated  $IT_{\rm max}$  versus depth along the vertical line. We see that a slight temperature decrease (about 30 of maximal 105) occurs in the GaN layer due to the low thermal conductivity of the sapphire substrate. If we separate the  $I_{\rm ds}$ - $V_{\rm ds}$  output charac-

FIG. 3. (a) Simulated and experimental  $I_{ds}$ - $V_{gs}$  of MOS-HEMT. Experiment (circles) and simulations with thermodynamics (dash line) and without thermodynamics (solid line) for  $V_{ds}$ =10 V. (b) Experimental  $I_{ds}$ - $V_{ds}$  of MOS-HEMT with  $V_{ds}$  from 0 to 10 V.

teristics into below and above saturation regions, the two regions meet where a segment of the 2DEG has become depleted, the mobility is decreased due to the enhanced scattering, and the drift velocity saturates. Above the voltage (at the above saturation regions), the current decreases with increasing  $V_{\rm ds}$ . Figure 5(a) clearly shows that the self-heating effects reduce the electron mobility at the drain-side gate edge, thus degrading the device performance and causing the NDC in the  $I_{\rm ds}$ - $V_{\rm ds}$  curve. This decrease correlates with the development of the localized "hot spot" [Fig. 5(b)] at the drain-side gate edge, where the self-heating effects are strongest. The self-heating effects can be eliminated or significantly reduced by a conventional heat-sink approach in the packaged power devices.

For a better description of the simulated behavior of the self-heating effects in the GaN-based MOS-HEMTs, we use a simple theoretical model<sup>36,37</sup> based on the heat dissipation and heat transfer in the GaN-based MOS-HEMTs.

The drain current as a function of the field can be determined from the coupled equations,

$$I = ne\,\mu(T_0 + \Delta T, E)WE,\tag{10}$$

$$\Delta T = \theta P_{\rm dis},\tag{11}$$

$$P_{\rm dis} = IEL, \tag{12}$$

where e is the electron charge,  $\mu$  is the electron mobility, n is the sheet electron concentration in the conducting channel, W is the device width, and E is the average electric field in the conducting channel. For simplicity, we take the thermal impedance  $\theta$  as a constant (about 325 C mm W<sup>-1</sup> on the sapphire).

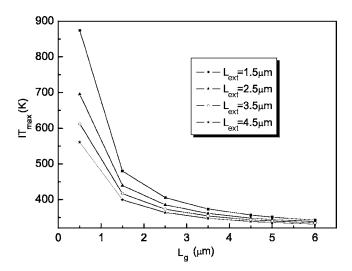

Figure 6 shows the dependence of the maximal lattice temperature  $(lT_{\rm max})$  on the gate length for the different source/drain extensions. As expected, the minimal  $\Delta T_{\rm max}$  ( $\Delta T_{\rm max} = lT_{\rm max} - T_0$ , where  $T_0$  is 300 K) are at the region of the long channel devices. We note that in each curve a relatively rapid temperature decrease at the short gate length region is followed by a somewhat slower decrease at the long gate length region under the same input voltage. It may be noted that although E is the same for the two devices, the total potential drop along the channel is slightly bigger for the shorter device due to its higher current. The increase in current with respect to the shorter device results in a larger

FIG. 4. Comparisons of (a) simulated  $I_{ds}$ - $V_{ds}$  results and (b) electron density in the channel with DG quasi-quantum-mechanical method (solid lines) and classical method (dashed lines) under the same condition.

FIG. 5. (Color online) Cross section of GaN-based MOS-HEMT around the drain-side gate edge showing (a) electron mobility contour map and (b) electron temperature contour map at  $V_{\rm ds}$ =30 V and  $V_{\rm gs}$ =3 V. (c) lT along the vertical line segment (dashed line) under the arrow in (b). Dimensions of (a) and (b) in  $\mu$ m.

dissipated Joule electric power  $(P_{\rm dis})$  [Eqs. (10)–(12)] across the source and drain contacts. From Eq. (11) we know that  $\Delta T$  increases linearly with  $P_{\rm dis}$ . Consequently, there is a relatively rapid decrease at the short gate length region.

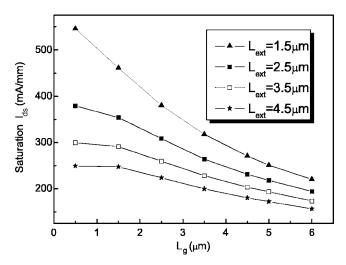

Figure 7 shows the dependence of the saturation drain current on the gate lengths for the different source/drain extension lengths. The shorter the channel is, the greater the reduction of the saturation  $I_{\rm ds}$  will be. The current reduction is caused by the increasing intrinsic normalized channel resistance  $R_{\rm ch} = V_{\rm ds} \times W_g/I_{\rm acc} \times L$ , where  $I_{\rm acc}$  is the accumulation current and L is the channel length  $(L = L_g + 2L_{\rm ext})$ . Comparing the dependence of  $I_{\rm ds}$  and  $\Delta T_{\rm max}$  on the gate lengths for the different  $L_{\rm ext}$ , we can easily get the optimal gate length (about 2.5  $\mu$ m) and source/drain extension (about 1.5  $\mu$ m) considering the self-heating effects.

FIG. 6. Dependence of maximal lattice temperature ( $lT_{\rm max}$ ) on the gate lengths for the different source/drain extension ( $L_{\rm ext}$ ) lengths at  $V_{\rm gs}$ =3 V and  $V_{\rm ds}$ =15 V.

### IV. HOT ELECTRON AND SELF-HEATING EFFECTS IN GAN-BASED MOS-HEMTS

High carrier concentrations of 2DEG and large values of the electron mobility and operation voltages make it necessary to distinguish the hot electron and self-heating effects for better understanding of the transport properties aimed to use the GaN-based MOS-HEMTs in high power and high temperature microelectronic applications. It is also very important to choose a suitable model for accurate and efficient (fast) physics-based device simulations to complement experiments. The hot electrons can overcome the potential barriers and be captured by the bulk traps in the barrier and bulk layers leading to the NDC in the output characteristics, <sup>19</sup> which is the so-called hot electron effects.

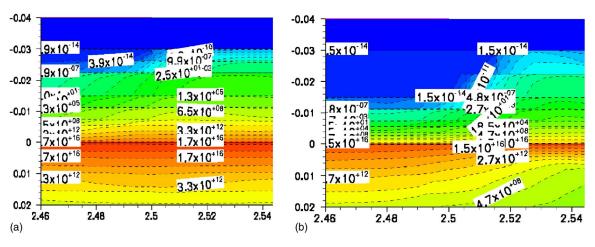

Figure 8 compares the simulated electron density contour map with the drift-diffusion and hot electron models at zero gate bias and 15 V drain bias. We can clearly see that in the drift-diffusion simulations electrons tend to be confined within the channel, while in the hot electron simulations the

FIG. 7. Dependence of saturation drain current  $(I_{\rm ds})$  on the gate lengths for the different source/drain extension  $(L_{\rm ext})$  lengths at  $V_{\rm gs}$ =3 V and  $V_{\rm ds}$ =15 V.

FIG. 8. (Color online) Cross section of GaN-based MOS-HEMT with electron density contour maps comparing results predicted by (a) hot electron and (b) simple drift-diffusion simulations at the drain-side gate edge. The AlGaN/GaN interface is at y=0; the AlGaN/Al<sub>2</sub>O<sub>3</sub> interface is at y=-0.03. Dimensions in  $\mu$ m.

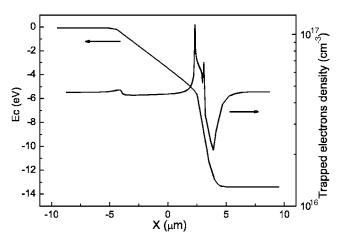

spreading of the hot electrons towards the AlGaN barrier and the GaN buffer is evident. At higher drain bias, the electrons become hotter; hence the wider flow spreading. This increase in drain bias also results in more trap levels in the bulk being occupied by the hot electrons. This extra negative charge subsequently lifts up the conduction band and decreases the 2DEG under the drain-side gate edge, leading to the formation of a potential barrier for the electron flow. However, for our long channel GaN-based MOS-HEMTs, there is no evident potential barrier formed at the drain-side gate edge. Figure 9 (left axis) shows the distribution of the trapped electrons at 5 nm away from the AlGaN/GaN interface at 10 V drain bias, which is where  $I_{\rm ds}$  saturates. The average trapped electron density is about  $7 \times 10^{16}$  cm<sup>-3</sup> smaller than that of the free 2DEG at the interface. Figure 9 (right axis) shows that no evident conduction band barrier is formed at the gate edge. Therefore, the trapped electrons make few contributions to the NDC in the long channel GaN-based MOS-HEMTs.

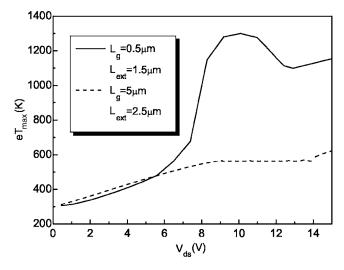

Figure 10 compares the maximal electron temperature  $(eT_{\rm max})$  of the long channel device:  $L_{\rm g}$ =5  $\mu$ m,  $L_{\rm ext}$ =2.5  $\mu$ m (dashed) and the short channel device:  $L_{\rm g}$ =0.5  $\mu$ m,

FIG. 9. Conduction band (left y axis) and trapped electron density (right y axis) vs x direction position for  $V_{\rm gs}$ =1 V and  $V_{\rm ds}$ =10 V.  $L_{\rm g}$ =5  $\mu{\rm m}$  and  $L_{\rm ext}$ =2  $\mu{\rm m}$ .

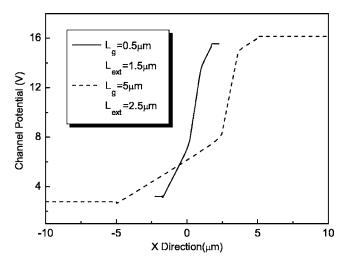

$L_{\rm ext}$ =1.5  $\mu{\rm m}$  (solid) in terms of the drain voltage for  $V_{\rm gs}$ =3 V. It shows that the drain voltage range (<6 V) is still below the field of well-developed hot electron regime expected from the theoretical predictions. 38,39 However, the electrons in the channel become dramatically hotter and reach the maximum at  $V_{\rm ds}$ =10 V when the drain voltage exceeds 6 V for the shorter channel device. It may also be noted that although  $V_{\rm ds}$  is the same for the two devices, the total voltage drop along the channel is slightly smaller for the shorter device due to its higher current. The increase in current with respect to the shorter channel device results in larger potential drops across the active region of the device (as shown in Fig. 11) and, consequently, in a slightly bigger  $eT_{\text{max}}$ . The nonlinearity of the shorter channel device in the  $eT_{\text{max}}$ - $V_{\text{ds}}$  is caused by the trapped hot electrons at the gate edge, which has been discussed in detail in Ref. 19, due to the bulk traps in AlGaN and GaN. The low maximal electron temperature for the long channel device implies that the hot electron model is not very important for self-heating simulations of long channel devices.

FIG. 10. Maximal electron temperature vs  $V_{\rm ds}$  for  $V_{\rm gs}{=}3$  V.  $L_{\rm g}{=}5~\mu{\rm m}$ ,  $L_{\rm ext}{=}2.5~\mu{\rm m}$  (dashed line) and  $L_{\rm g}{=}0.5~\mu{\rm m}$ ,  $L_{\rm ext}{=}1.5~\mu{\rm m}$  (solid line).

FIG. 11. Electrostatic potential of the conduction channel vs x direction position for the devices simulated in Fig. 8 for  $V_{\rm gs}$ =3 V and  $V_{\rm ds}$ =15 V.  $L_g$ =5  $\mu$ m,  $L_{\rm ext}$ =2.5  $\mu$ m (solid line) and  $L_g$ =0.5  $\mu$ m,  $L_{\rm ext}$ =1.5  $\mu$ m (dashed line).

## V. EFFECTS OF STATIC INTERFACE CHARGES AND TRAPS

It is generally accepted that the empty donorlike traps generated by the process damage positively charge AlGaN interface under the gate. As mentioned in Sec. II, the interface charges are induced by the polarization effects of the wurtzite group-III nitride heterointerface. In order to visualize the interface-related effects, we ran the static simulations with the different donor trap and charge densities (negative charge for the  $Al_2O_3/AlGaN$  interface with the theoretical computation). Unlike the conventional GaNbased HEMT, our  $Al_2O_3/AlGaN/GaN$ -based MOS-HEMT has an interface ( $Al_2O_3/AlGaN$ ) under the gate contact. Therefore, it is very important to investigate the inner mechanisms of the interface-state-related effects on the MOS-HEMT.

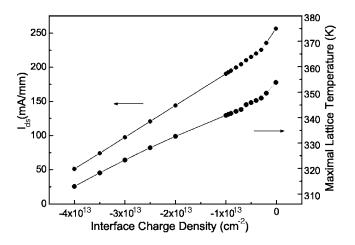

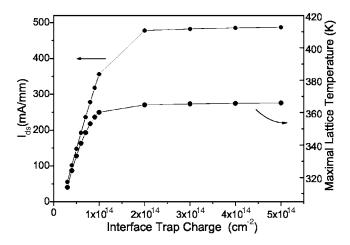

The interface states assumed in our model consist of a fixed interface charge and an interface trap of a uniform distribution at the Al<sub>2</sub>O<sub>3</sub>/AlGaN interface. As shown in Fig. 12, a reduction in the drain current is obtained when an order of

FIG. 12. Drain current (left y axis) and maximal lattice temperature (right y axis) vs interface charge density for  $V_{\rm gs}$ =0 V and  $V_{\rm ds}$ =15 V.  $L_{\rm g}$ =5  $\mu$ m and  $L_{\rm ext}$ =2  $\mu$ m.

FIG. 13. Drain current (left y axis) and maximal lattice temperature (right y axis) vs interface trap charge for  $V_{\rm gs}$ =0 V and  $V_{\rm ds}$ =15 V.  $L_{\rm g}$ =5  $\mu$ m,  $L_{\rm ext}$ =2  $\mu$ m.

magnitude increase of the negative interface charge is assumed at the Al<sub>2</sub>O<sub>3</sub>/AlGaN interface. The drastic reduction of the channel current occurs in the areas at the interface where the fixed interface charge is defined—the interface acts as a virtual gate located between the contacts, <sup>43</sup> as well as under the gate. Another reason for the channel current reduction is the increase in hole concentration next to the interface where the interface charge is introduced (we neglect the donor trap effects which are discussed later). As the magnitude of the interface charge density increases, the holes are attracted towards the interface, where they play an important role in neutralizing the negative interface charges. From the above discussions, we can conclude that the presence of the fixed charge at the interface can be directly responsible for the current collapse in the GaN-based MOS-HEMTs. Figure 12 also shows that the maximal lattice temperature decreases down to 7.36% for the interface charge density of  $-4 \times 10^{13}$  cm<sup>-2</sup>. We also note that the selfheating effects are suppressed due to the neutralization of the attracted holes by the increasing negative interface charge density. However, the excessive increase of the charge density decreases the drain current because the virtual gate becomes too "thick."

Figure 13 shows the drain current and the maximal lattice temperature versus the interface trap charge for  $V_{\rm gs}$ =3 V and  $V_{\rm ds}$ =15 V. The drain current increases up to 92%for the interface trap charge  $\ge 9 \times 10^{13}$  cm<sup>-2</sup>. The donor traps, which are partially ionized, create a positive step in the gate voltage, which further ionizes the donor traps and increases the drain current. Our results indicate that the drain current is sensitive to the interface donor trap charge, which reduces the net charges at the Al<sub>2</sub>O<sub>3</sub>/AlGaN interface. The net charges are a summation of the ionized donor traps and negative interface charges. 44,45 As expected, a similarity in the drain current response is obtained when an increase in the trap charge is used in the model. From Eq. (12), we know that the increase of the drain current under the same electric field causes the correspondingly larger dissipated Joule electric power, thus increasing self-heating.

The above discussion gives a clear picture of the effects

FIG. 14. (Color online) The pinch off state of GaN-based MOS-HEMT under a positive drain bias.

of the donor traps and polarization interface charges on the operation of the GaN-based MOS-HEMT. When the gate is negatively biased and the drain is positively biased (as shown in Fig. 14), the interface traps at the Al<sub>2</sub>O<sub>3</sub>/AlGaN are filled with electrons injected from the gate during pinch off. 41,46 At the reverse gate bias, although the gate leakage current of the MOS-HEMTs is lower than that of the conventional HEMTs, 11 it is reasonable to assume that some of the electrons can still be injected from the gate through Al<sub>2</sub>O<sub>3</sub>. With the surface traps filled with the injected electrons, the channel is vertically depleted to keep the system neutral, instead of being laterally depleted by the drain bias. Since there is no lateral depletion in the channel, the electric field peak in the x direction at the drain-side gate edge is alleviated. The electric field in the depletion region is a combination of the vertical polarization field  $(E_p)$  and the constant lateral bias electric field  $(E_x)$ . When the gate and the drain are positively biased (which is the on state of the switching device), the trapped electrons escape from the traps leading to the disappearance of the vertical depletion and the recovery of density of the 2DEG in the channel. Finally, the current passes through the channel, and the device is turned on.

#### VI. CONCLUSION

High performance GaN-based MOS-HEMTs have been fabricated with Al<sub>2</sub>O<sub>3</sub> gate dielectrics. We have accurately simulated the self-heating effects of the GaN-based MOS-HEMTs. The simulation results were found to be in good agreement with the experimental data for Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN MOS-HEMTs on a sapphire substrate with a 5  $\mu$ m gate length. Both the simulated and experimental results show that the transfer characteristics are not greatly affected by the self-heating effects when operating below a 10 V drain voltage. The simulated  $I_{ds}$ - $V_{ds}$  current is suppressed by approximately 9.6% due to carrier confinement when the quantum approach is chosen. The quantum calculations clearly show a significant penetration of the electron wave function from the 2D gas into threedimensional states in AlGaN and GaN. We also note that the data from the quantum method agrees more closely to that of the experimental measurements.

The dependence of the maximal lattice temperature and saturation drain current on the gate length with different source/drain extension lengths clearly reveals a design trade-off between the operation drain current and the self-heating. Finally, the optimal gate length (about 2.5  $\mu$ m) and the source/drain extension length (about 1.5  $\mu$ m) are extracted from the simulation data. The presence of the interface charges and traps are directly responsible for the observed current collapse and device switching in the GaN-based MOS-HEMTs. Our results allow us to identify the nature of the donor traps affecting the interface net charge. The self-heating is also strongly affected due to the fluctuation of the interface states.

#### **ACKNOWLEDGMENTS**

This work was supported in part by a grant from the State Key Program for Basic Research of China (2001CB61040), National Natural Science Foundation of China (60476040 and 60576068) and Creative Group (60221502), Key Fund of Chinese National Natural Science Foundation (10234040), and Ground Fund of Shanghai Science and Technology Foundation (05DJ14003). The authors appreciate Aaron Franklin for critical reading of the manuscript.

<sup>1</sup>M. Asif Khan, X. Hu, G. Sumin, A. Lunev, J. Yang, R. Gaska, and M. S. Shur, IEEE Electron Device Lett. 21, 63 (2000).

<sup>2</sup>M. Asif Khan, X. Hu, A. Tarakji, G. Simin, J. Yang, R. Gaska, and M. S. Shur, Appl. Phys. Lett. 77, 1339 (2000).

<sup>3</sup>G. Simon *et al.*, Electron. Lett. **36**, 2043 (2000).

<sup>4</sup>A. Koudymov, X. Hu, K. Simin, G. Simin, M. Ali, J. Yang, and M. Asif Khan, IEEE Electron Device Lett. **23**, 449 (2002).

<sup>5</sup>G. Simin et al., IEEE Electron Device Lett. 23, 458 (2002).

<sup>6</sup>G. Simon et al., IEEE Electron Device Lett. 22, 53 (2001).

<sup>7</sup>X. Hu, A. Koudymov, G. Simon, J. Yang, M. Asif Khan, A. Tarakji, M. S. Shur, and R. Gaska, Appl. Phys. Lett. **79**, 2832 (2000).

<sup>8</sup>S. Ootomo, T. Hashizume, and H. Hasegawa, Phys. Status Solidi C 1, 90 (2002)...

<sup>9</sup>T. Hashizume, S. Ootomo, and H. Hasegawa, Appl. Phys. Lett. 83, 2952 (2003).

<sup>10</sup>R. Mehandru *et al.*, Appl. Phys. Lett. **82**, 2530 (2003).

<sup>11</sup>P. D. Ye, B. Yang, K. K. Ng, J. Bude, G. D. Wilk, S. Halder, and J. C. M. Hwang, Appl. Phys. Lett. **86**, 063501 (2005).

<sup>12</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

<sup>13</sup>S. W. Huang and J. G. Hwu, IEEE Trans. Electron Devices 50, 1658 (2003).

<sup>14</sup>Y. F. Wu, B. P. Keller, S. Keller, D. Kapolnek, S. P. Denbaars, and U. K. Mishra, IEEE Electron Device Lett. 17, 455 (1996).

<sup>15</sup>Y. F. Wu, B. P. Keller, S. Keller, D. Kapolnek, P. Kozodoy, S. P. Denbaars, and U. K. Mishra, Solid-State Electron. 41, 1569 (1997).

<sup>16</sup>L. F. Eastman et al., IEEE Trans. Electron Devices 48, 479 (2001).

<sup>17</sup>J. D. Albrecht, P. P. Ruden, S. C. Binari, and M. G. Ancona, IEEE Trans. Electron Devices 47, 479 (2001).

<sup>18</sup>I. Ahmad, V. Kasisomayajula, M. Holtza, J. M. Berg, S. R. Kurtz, C. P. Tigges, A. A. Allerman, and A. G. Baca, Appl. Phys. Lett. 86, 173503 (2005).

<sup>19</sup>N. Braga, R. Gaska, R. Mickevicius, M. S. Shur, X. Hu, M. A. Khan, G. Simin, and J. Yang, J. Appl. Phys. **95**, 6409 (2004).

<sup>20</sup>N. Braga, R. Gaska, R. Mickevicius, M. S. Shur, X. Hu, M. A. Khan, G. Simin, and J. Yang, Appl. Phys. Lett. 85, 4780 (2004).

<sup>21</sup>DESSIS ISE TCAD Manual, Release 10.06 (ISE Integrated Systems Engineering AG, Zurich, 2005).

<sup>22</sup>A. D. Bykhovski, R. Gaska, and M. S. Shur, Appl. Phys. Lett. **73**, 3577 (1998).

<sup>23</sup>P. M. Asbeck, E. T. Yu, S. S. Lau, G. J. Sullivan, J. Van Hove, and J. M. Redwing, Electron. Lett. 33, 1230 (1997).

- <sup>24</sup>E. T. Yu, G. J. Sullivan, P. M. Asbeck, C. D. Wang, D. Qiao, and S. S. Lau, Appl. Phys. Lett. **71**, 2794 (1997).

- <sup>25</sup> M. B. Nardelli, K. Rapcewicz, and J. Bernholc, Appl. Phys. Lett. 71, 3135 (1997).

- <sup>26</sup>T. Takeuchi, H. Takeuchi, S. Sota, H. Sakai, H. Amano, and I. Akasaki, Jpn. J. Appl. Phys., Part 1 36, 177 (1997).

- <sup>27</sup>O. Ambacher *et al.*, J. Appl. Phys. **85**, 3222 (1999).

- <sup>28</sup>O. Ambacher *et al.*, J. Appl. Phys. **87**, 334 (2000).

- <sup>29</sup>E. T. Yu, G. J. Sullivan, P. M. Asbeck, C. D. Wang, D. Qiao, and S. S. Lau, Appl. Phys. Lett. **71**, 2794 (1997).

- <sup>30</sup>M. G. Ancona and H. F. Tiersten, Phys. Rev. B **35**, 7959 (1987).

- <sup>31</sup>D. K. Ferry and J. R. Zhou, Phys. Rev. B **48**, 7944 (1993).

- <sup>32</sup>X. H. Wu, L. M. Brown, D. Kapolnek, S. Keller, B. Keller, S. P. Den-Baars, and J. S. Speck, J. Appl. Phys. **80**, 3228 (1996).

- <sup>33</sup>P. B. Klein, S. C. Binari, K. Ikossi, A. E. Wickenden, D. D. Koleske, and R. L. Henry, Appl. Phys. Lett. **79**, 3527 (2001).

- <sup>34</sup>J. Zou, D. Kotchetkov, A. A. Balandin, D. I. Florescu, and F. H. Pollak, J. Appl. Phys. **92**, 2534 (2002).

- <sup>35</sup>R. Gaska, Q. Chen, J. Yang, A. Osinsky, M. Asif Khan, and M. S. Shur, IEEE Electron Device Lett. 18, 492 (1997).

- <sup>36</sup>S. A. Vitusevich *et al.*, Appl. Phys. Lett. **82**, 748 (2003).

- <sup>37</sup>R. Gaska, A. Osinsky, J. W. Yang, and M. S. Shur, IEEE Electron Device Lett. 19, 89 (1998).

- <sup>38</sup>E. A. Barry, K. W. Kim, and V. A. Kochelap, Appl. Phys. Lett. **80**, 2317 (2002).

- <sup>39</sup>T. H. Yu and K. F. Brennan, J. Appl. Phys. **89**, 3827 (2001).

- <sup>40</sup>I. P. Smorchkova et al., J. Appl. Phys. **86**, 4520 (1999).

- <sup>41</sup>H. Hasegawa, T. Inagaki, S. Ootomo, and T. Hashizume, J. Vac. Sci. Technol. B 21, 1844 (2003).

- <sup>42</sup>J. Kotani, T. Hashizume, and H. Hasegawa, J. Vac. Sci. Technol. B 22, 2179 (2004).

- <sup>43</sup>R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, IEEE Trans. Electron Devices 48, 560 (2001).

- <sup>44</sup>J. M. Tirado, J. L. Sanchez-Rojas, and J. I. Izpura, Semicond. Sci. Technol. 20, 864 (2005).

- <sup>45</sup>W. Saito, M. Kuraguchi, Y. Takada, K. Tsuda, I. Omura, and T. Ogura, IEEE Electron Device Lett. **52**, 159 (2005).

- <sup>46</sup>N. Q. Zhang, B. Moran, S. P. DenBaars, U. K. Mishra, X. W. Wang, and T. P. Ma, Tech. Dig. - Int. Electron Devices Meet. 2001, 589.